Digital Signal Processing & VLSI Systems

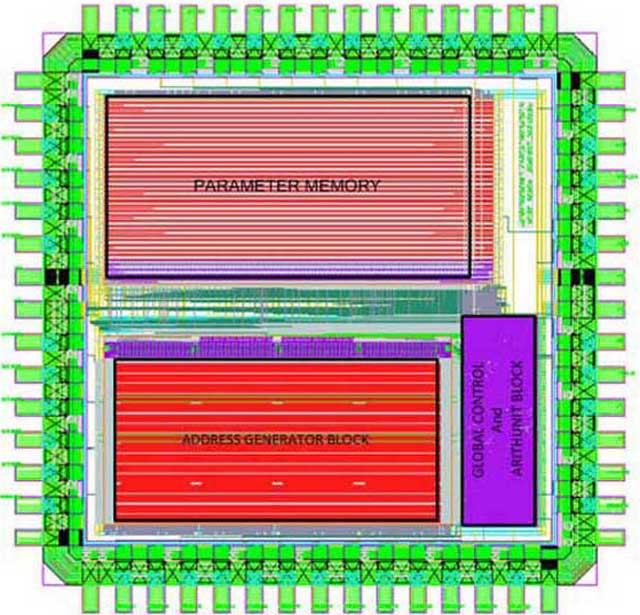

This research topic has as main aim the efficient implementation of digital integrated circuits on ASICs at several abstraction levels: at a transistor level, designing basic digital cells with a full-custom methodology; at a gate level, finding optimum solutions for combinational and sequential circuits; at a circuit level, developing architectures and timing strategies. Transversal optimization mechanisms are employed in all these implementations, such as for instance, switching activity analysis, minimization of power consumption, low switching-noise generation, design of cells with data-independent power consumption, design for high-speed applications, etc.

Work in this topic faces:

Main results achieved include:

P. Brox, M.C. Martínez-Rodríguez, E. Tena-Sánchez, I. Baturone and A.J. Acosta, "Application specific integrated circuit solution for multi-input multi-output piecewise-affine functions", International Journal of Circuit Theory and Applications, vol. 44, no. 1, pp. 4-20, 2016 » doi

M.C. Martínez-Rodríguez, P. Brox and I. Baturone, "Digital VLSI implementation of piecewise-affine controllers based on lattice approach", IEEE Transactions on Control Systems Technology, vol. 23, no. 3, pp. 842-854, 2015 » doi

A.J. Acosta, "Low Power and Security Trade-off in Hardware: From True Random Number Generators to DPA Resilience", Conferencia invitada al Energy Secure Systems Architecture Workshop ISCA 2014, Minnessotta, USA

P. Brox, J. Castro-Ramírez, M.C. Martínez-Rodríguez, E. Tena, C.J. Jiménez, I. Baturone and A.J. Acosta, "A Programmable and Configurable ASIC to Generate Piece-wise-Affine Functions Defined Over General Partitions", IEEE Trans. on Circuits and Systems I: Regular Papers, vol. 60, no. 12, pp. 3182-3194, 2013 » doi

A.J. Acosta, I. Baturone, J. Castro-Ramírez, C.J. Jiménez, P. Brox and M.C. Martínez-Rodríguez. Method for generating piecewise-affine multivariable functions with on-line computation of the search tree and device for implementing same. 2012 » pdf

INTERVALO: Integration and validation in laboratory of countermeasures against side-channel attacks in microelectronic cryptocircuits (TEC2016-80549-R)

PI: Antonio J. Acosta Jiménez / Carlos J. Jiménez Fernández

Funding Body: Min. de Economía, Industria y Competitividad

Dec 2016 - Dec 2019

CESAR: Secure microelectronic circuits against side-channel attacks (TEC2013-45534-R)

PI: Antonio J. Acosta Jiménez / Carlos J. Jiménez Fernández

Funding Body: Min. de Economía y Competitividad

Jan 2014 - Dec 2016

WEBSITE

CITIES: Integrated circuits for transmitting secure information (TEC2010-16870)

PI: Carlos J. Jiménez Fernández

Funding Body: Min. de Ciencia e Innovación

Jan 2011 - Sep 2014

WEBSITE

MOBY-DIC: Model-based synthesis of digital electronic circuits for embedded control (EC-IST-VIIPM no.-248858)

PI: Antonio J. Acosta Jiménez

Funding Body: 7th Framework Programme, European Commission

Dec 2009 - Nov 2013

CRIPTO-BIO: Microelectronic design for crypto-biometric authentication (P08-TIC-03674)

PI: Iluminada Baturone Castillo

Funding Body: Junta de Andalucía - Proyectos de Excelencia

Jan 2009 - Dec 2013

WEBSITE