Analog Signal Processing

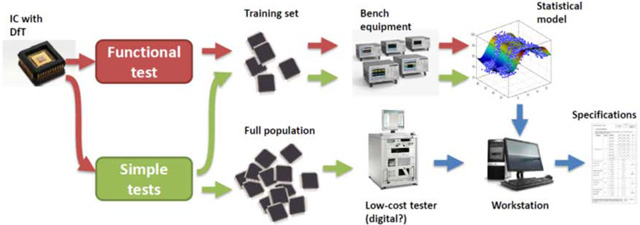

This research line gathers all the activities related to the development of test techniques. These can be low-cost functional approaches whose goal is the direct estimation of the specified performance. Other structural approaches (defect-oriented or indirect) make more use of Design-for-Testability features and rely on the consideration that the circuit is correct by design. As a result they are more focused on the detection of spot defects or unexpectedly excessive parametric deviations.

In both cases, embedded test techniques (commonly called Built-In Self-Test or BIST) are of particular interest to reduce test plan complexity, to enable the test of IP blocks with limited accessibility within a System-on-Chip (SoC) or even to enable in-field testing (which increases system-level diagnosis capability).

Our most recent research themes in this line are:

G. Leger and M. J. Barragan, "Brownian distance correlation-directed search: A fast feature selection technique for alternate test", Integration, the VLSI Journal, vol. 55, pp. 401414, Sep 2016 » doi

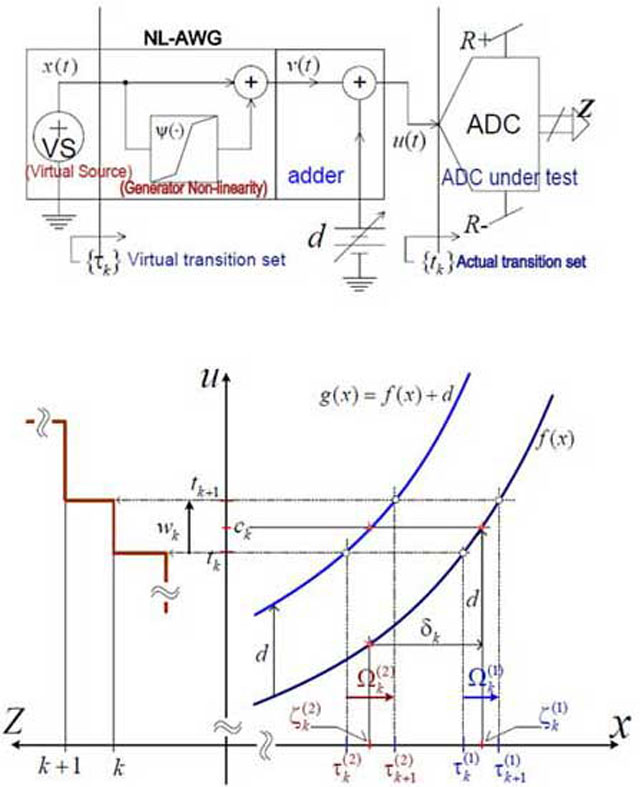

A.J. Gines E. Peralias, G. Leger, A. Rueda, G. Renaud, M.J. Barragan and S. Mir, "Linearity test of high-speed high-performance ADCs using a self-testable on-chip generator", IEEE European Test Symposium (ETS), Amsterdam, 2016 » doi

M.J. Barragan and G. Leger, "A Procedure for Alternate Test Feature Design and Selection", IEEE Design & Test, vol. 32, no. 1, pp. 1825, Feb 2015 » doi

M.J. Barragan, G. Leger, D. Vazquez and A. Rueda, "On-chip sinusoidal signal generation with harmonic cancelation for analog and mixed-signal BIST applications", Analog Integrated Circuits and Signal Processing, vol. 82, pp. 67-79, 2015 » doi

Best Special session award: M.J. Barragan, G. Leger, F. Azais, R.D. Blanton, A. D. Singh and S. Sunter, "Special session: Hot topics: Statistical test methods," VLSI Test Symposium (VTS), Napa (USA), 2015 » doi

IndieTEST: Indirect Test solutions for analog, mixed-signal and RF integrated systems (PICS CNRS)

PI: Gildas Léger (CSIC) / Manuel Barragán (CNRS)

Funding Body: CSIC & CNRS

Jan 2017 - Dec 2019

n-PATETIC: New paradigms for testing mixed-signal integrated circuits (TEC2015-68448-R)

PI: Adoración Rueda Rueda

Funding Body: Min. de Economía y Competitividad

Jan 2016 - Dec 2018

DANTE: Adapting Mixed-signal and RF ICs Design and Test to Process and Evironment Variability (TEC2011-28302)

PI: Adoración Rueda Rueda

Funding Body: Min. de Ciencia e Innovación

Jan 2012 - Dec 2015

ACATEX: Self-calibration and self-test of analog, mixed-signal and radio frecuency circuits (P09-TIC-5386)

PI: Adoración Rueda Rueda

Funding Body: Junta de Andalucía - Proyectos de Excelencia

Mar 2010 - Feb 2014

TOETS: Towards One European Test Solution

PI: José L. Huertas Díaz

Funding Body: CE: CATRENE European Program - CT302

Dec 2009 - Nov 2011