Nanoelectronics and Emerging Technologies

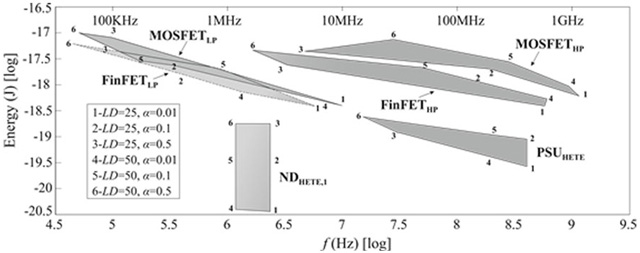

Main research objective is the development, analysis and design of circuits using emerging devices and/or nonconventional logic models, with emphasis on applications with severe constraints on power or energy like IoT. In particular, we explore circuits based on resonant tunel diodes (RTDs), tunel transistors (TFETs and SymFETs) or devices integrating phase transition (Hyper-FETs, VO2). The distinguishing features of these devices is exploited to obtain circuits competitive with respect to their CMOS counterparts in terms of speed, power, energy or area or exhibiting better trade-offs among those criteria. From the logic point of view, we study threshold logic and more recently oscillator-based computing.

Main recent activities in this line include:

M.J. Avedillo, J.M. Quintana and J. Núñez, "Phase Transition Device for Phase Storing", IEEE Transactions on Nanotechnology, vol. 19, pp 107-112, 2020 » doi

M. Jiménez, J. Núñez and M.J. Avedillo, "Hybrid Phase Transition FET Devices for Logic Computation", IEEE Journal on Exploratory Solid-State Computational Devices and Circuits, vol. 6, no. 1, pp 1-8, 2020 » doi

J. Núñez and J.M. Avedillo, "Approaching the Design of Energy Recovery Logic Circuits using Tunnel Transistors", IEEE Transactions on Nanotechnology, vol. 19, pp 500-507, 2020 » doi

J. Núñez and M.J. Avedillo, "Power and Speed Evaluation of Hyper-FET Circuits", IEEE Access, vol. 7, pp 6724-6732, 2019 » doi

J. Nuñez and M.J. Avedillo, "Reducing the Impact of Reverse Currents in Tunnel FET Rectifiers for Energy Harvesting Applications", IEEE Journal of the Electron Devices Society, vol. 5, no. 6, pp. 530-534, 2017 » doi

NEURONN: Two-Dimensional Oscillatory Neural Networks for Energy Efficent Neuromorphic computing (H2020-871501)

PI: Bernabé Linares Barranco

Funding Body: European Union

Jan 2020 - Dec 2022

PULPOSS: Processing for Ultra Low POwer using Steep Slope devices: circuits and arquitectures (TEC2017-87052-P)

PI: María J. Avedillo de Juan / José M. Quintana Toledo

Funding Body: Min. de Economía y Competitividad

Jan 2018 - Dec 2020

NACLUDE: Nano-architectures for logic computing using emergent devices (TEC2013-40670-P)

PI: Jose M. Quintana Toledo / María J. Avedillo de Juan

Funding Body: Min. de Economía y Competitividad

Jan 2014 - Dec 2017

RTDs: Architectures and circuits for logic and non-linear applications using RTDs (TEC2010-18937)

PI: María J. Avedillo de Juan

Funding Body: Min. de Ciencia e Innovación

Jan 2011 - Dec 2014

QUDOS: Quantum Tunneling Device Technology on Silicon (IST-2001-32358)

PI: Werner Prost / WP Coordinator: José M. Quintana Toledo

Funding Body: European Comission

Jan 2002 - Dec 2004