Implementing innovative concepts in silicon

Through a laser maze and cryptographic challenges, researchers from the center brought key concepts of digital protection closer to hundreds of students from all over Europe.

March 26, 2026

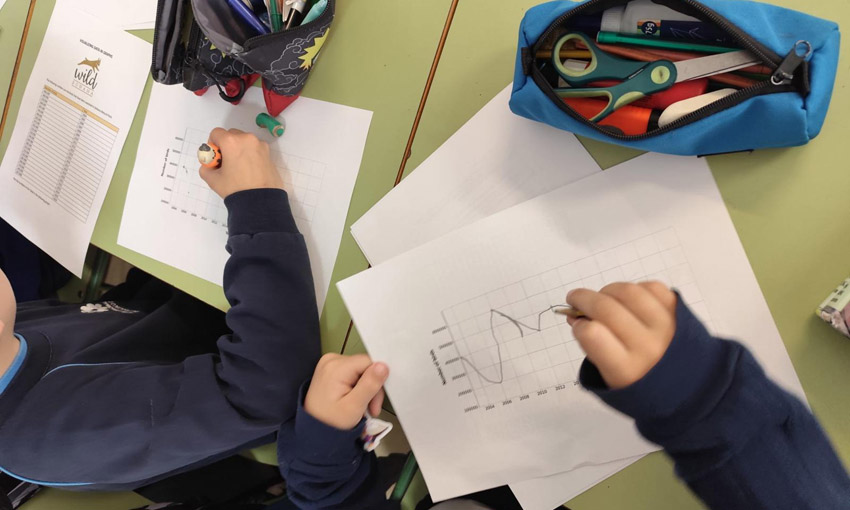

IMSE researchers bring science outreach to schools to mark International Mathematics Day.

March 16, 2026

At IMSE we carry out several activities to highlight the role of the researchers at our center.

March 2, 2026

"Science is Wonderful!", the International Science Fair organized by the European Commission, will be held in Brussels on March 18, 19 and 20, 2026, and will once again feature, for the third consecutive year, the participation of a team of researchers from the Instituto de Microelectrónica de Sevilla (IMSE-CNM).

November 3, 2025

The research talent of IMSE shines once again with the "Leonardo Torres Quevedo" Award granted to Pablo Navarro for his Master's Thesis that delves into the security and efficiency of cryptographic algorithms.

October 31, 2025

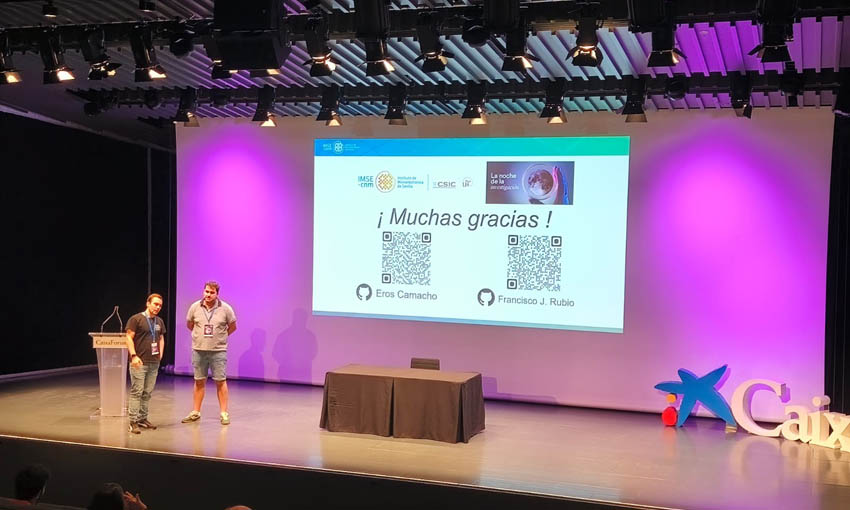

The Instituto de Microelectrónica de Sevilla connected with the public through two activities that combined entertainment and scientific learning, bringing microelectronics and cybersecurity closer together in an interactive and participatory manner.

October 3, 2025

Assessment of an FPGA Implementation of a Hybrid PUF Based on a Configurable Transient Effect Ring Oscillator and Ring Oscillator (TERORO-PUF)

A. Casado-Galán, J. Núñez, E. Tena-Sánchez, F.E. Potestad-Ordóñez and A.J. Acosta-Jiménez

Journal Paper · Electronics, vol. 15, no. 3, article 661, 2026

MDPI ISSN: 2079-9292

abstract

doi

Enhancing the performance of HfO2-based memristors with a thin Al2O3 layer: a comparative study

M. Shooshtari, T. Serrano Gotarredona and B. Linares-Barranco

Journal Paper · Journal of Physics D: Applied Physics, vol. 58, no. 45, 2025

IOP Science

abstract

doi

A Side-Channel Protected and High-Performance Hardware Implementation for EdDSA25519

P. Navarro-Torrero, E. Camacho-Ruiz, M.C. Martínez-Rodríguez and P. Brox

Journal Paper · IEEE Access Vol 13

IEEE ISSN: 2169-3536

abstract

doi

Workload Compression Techniques to Scale Defect-Centric BTI Models to the Circuit Level

A. Santana-Andreo, V.M. van Santen, R. Castro-López, E. Roca, H. Amrouch and F.V. Fernández

Journal Paper · IEEE Transactions on Circuits and Systems I: Regular Papers (Early Access), 2025

IEEE ISSN: 1549-8328

abstract

doi

Our main area of specialization is the design of CMOS analog and mixed-signal integrated circuits and their use in different application contexts such as wireless communications, data conversion, smart imagers & vision sensors, biomedical devices, cybersecurity, neuromorphic computing and space technologies.

The IMSE-CNM staff consists of approximately one hundred people, including scientists and support personnel. IMSE-CNM employees are involved in advancing scientific knowledge, designing high level scientific-technical solutions and in technology transfer.