Implementando conceptos innovadores en silicio

A través de un laberinto láser y retos criptográficos, investigadores del centro acercaron conceptos clave de protección digital a cientos de estudiantes procedentes de toda Europa.

26 Marzo 2026

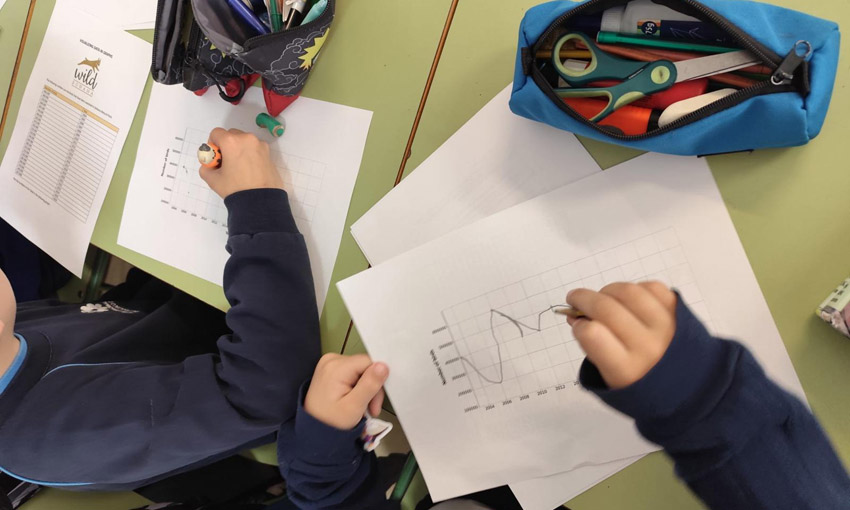

Investigadores del IMSE llevan la divulgación científica a centros educativos con motivo del Día Internacional de las Matemáticas.

16 Marzo 2026

Desde el IMSE llevamos a cabo varias actividades para poner en valor en papel de las investigadoras de nuestro centro.

2 Marzo 2026

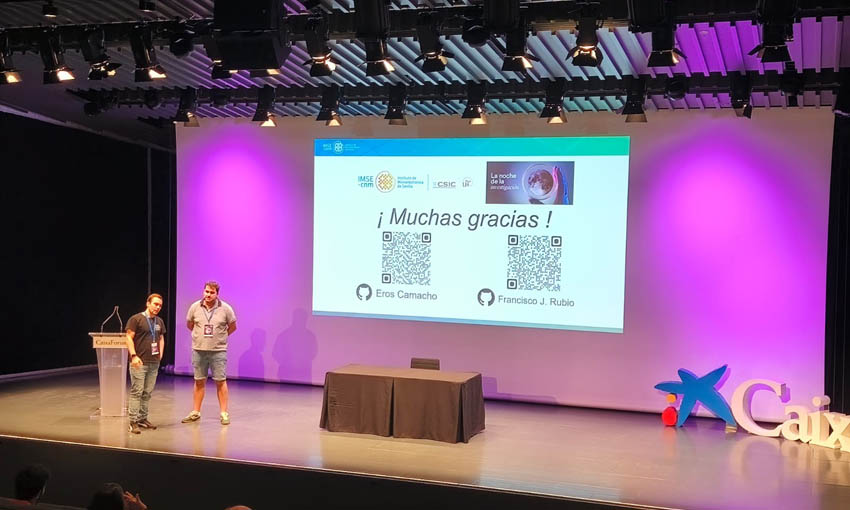

"Science is Wonderful!", la Feria Internacional de la Ciencia organizada por la Comisión Europea, se celebrará en Bruselas los próximos 18, 19 y 20 de marzo de 2026, y volverá a contar por tercer año consecutivo con la participación de un equipo de investigadores del Instituto de Microelectrónica de Sevilla (IMSE-CNM).

3 Noviembre 2025

El talento investigador del IMSE vuelve a destacar con el Premio "Leonardo Torres Quevedo" concedido a Pablo Navarro por su Trabajo de Fin de Máster que profundiza en la seguridad y eficiencia de algoritmos criptográficos.

31 Octubre 2025

El Instituto de Microelectrónica de Sevilla conectó con la ciudadanía a través de dos actividades que combinaron entretenimiento y aprendizaje científico, acercando la microelectrónica y la ciberseguridad de manera interactiva y participativa.

3 Octubre 2025

Robust and Scalable Cell-Based 65-nm CMOS RO-PUF Implementation

P. Ortega-Castro, E. Camacho-Ruiz, J.M. Mora-Gutiérrez, P. Brox and M.C. Martínez-Rodríguez

Journal Paper · IEEE Open Journal of the Solid-State Circuits Society (Early Access)

IEEE ISSN: 2644-1349

resumen

doi

Assessment of an FPGA Implementation of a Hybrid PUF Based on a Configurable Transient Effect Ring Oscillator and Ring Oscillator (TERORO-PUF)

A. Casado-Galán, J. Núñez, E. Tena-Sánchez, F.E. Potestad-Ordóñez and A.J. Acosta-Jiménez

Journal Paper · Electronics, vol. 15, no. 3, article 661, 2026

MDPI ISSN: 2079-9292

resumen

doi

Enhancing the performance of HfO2-based memristors with a thin Al2O3 layer: a comparative study

M. Shooshtari, T. Serrano Gotarredona and B. Linares-Barranco

Journal Paper · Journal of Physics D: Applied Physics, vol. 58, no. 45, 2025

IOP Science

resumen

doi

A Side-Channel Protected and High-Performance Hardware Implementation for EdDSA25519

P. Navarro-Torrero, E. Camacho-Ruiz, M.C. Martínez-Rodríguez and P. Brox

Journal Paper · IEEE Access Vol 13

IEEE ISSN: 2169-3536

resumen

doi

El área de especialización del Instituto es el diseño de circuitos integrados analógicos y de señal mixta en tecnología CMOS, así como su uso en diferentes contextos de aplicación tales como dispositivos biomédicos, comunicaciones inalámbricas, conversión de datos, sensores de visión inteligentes, ciberseguridad, computación neuromórfica y tecnología espacial.

La plantilla del IMSE-CNM está formada por unas cien personas, entre personal científico y de apoyo, que participan en el avance del conocimiento, la generación de diseños de alto nivel científico-técnico y la transferencia de tecnología.