Digital Signal Processing & VLSI Systems

This research line is focused on the design of digital embedded systems implemented on programmable devices (FPGAs), using intellectual property (IP) modules. The aim is to solve problems related to size constraints, power consumption and computation that characterize such systems, as well as to provide the tools and design methodologies that facilitate and accelerate its development. The highlights of the developed solutions are the design of specific processing architectures, hardware/software codesign techniques, the use of reconfigurable devices, and the employment of Intellectual Property (IP) modules for reusability. The transversal nature of this research line allows that its results can be used in different application domains related to other research activities of the group.

The topics of interest that are covered by this research line are:

E. Calvo-Gallego, P. Brox and S. Sanchez-Solano, "Low-cost dedicated hardware IP modules for background subtraction in embedded vision systems", Journal of Real-Time Image Processing, vol. 12, no. 4, pp. 681-695, 2016 » doi

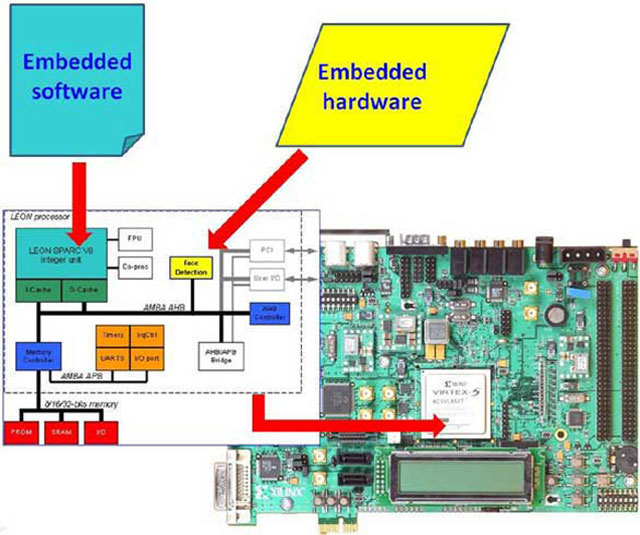

M.J. Avedillo, A. Barriga, L. Acasandrei and J.M. Calahorro, "Hardware-software embedded face recognition system", International Conferences in Central Europe on Computer Graphics, Visualization and Computer Vision (WSCG), Pilzen, Czech Republic, 2016

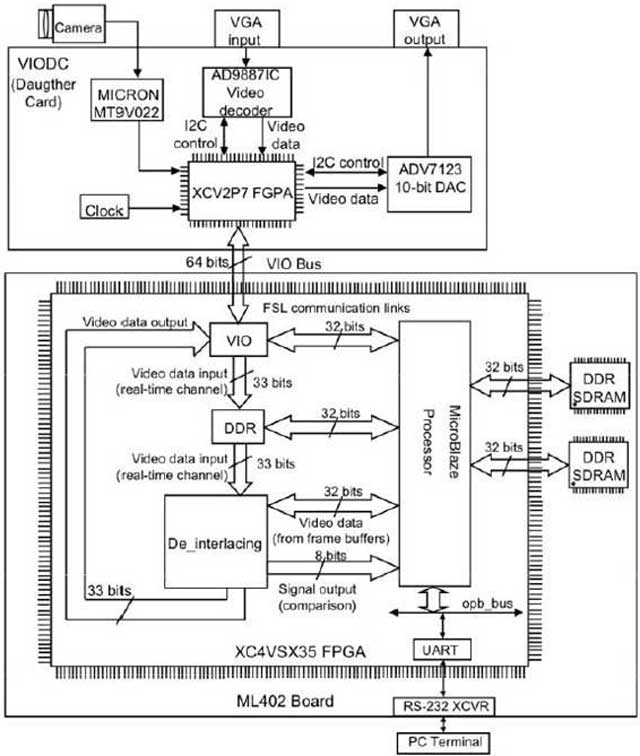

P. Brox, I. Baturone and S. Sánchez-Solano, "Fuzzy logic-based embedded system for video de-interlacing", Applied Soft Computing, vol. 14, part C, pp. 338-346, 2014 » doi

M. Brox, S. Sánchez-Solano, E. del Toro, P. Brox and F.J. Moreno-Velo, "CAD tools for hardware implementation of embedded fuzzy systems on FPGAs", IEEE Transactions on Industrial Informatics, Special Section on Embedded and Reconfigurable Systems, vol. 9, no. 3, pp. 1635-1644, 2013 » doi

ID-EO: Design of crypto-biometric hardware for video encryption and authentication (TEC2014-57971-R)

PI: Iluminada Baturone Castillo / Piedad Brox Jiménez

Funding Body: Min. de Economía y Competitividad

Jan 2015 - Dec 2018

WEBSITE

SENIAC: Security in interconnected devices by injection of authentication and ciphering algorithms (RTC-2014-2932-8)

PI: Iluminada Baturone Castillo

Funding Body: Min. de Economía y Competitividad

Oct 2014 - Mar 2017

WEBSITE

SEIs: Hardware design for embedded systems in intelligent environments (TEC2011-24319)

PI: Santiago Sánchez Solano

Funding Body: Min. de Ciencia e Innovación

Jan 2012 - Sep 2015

WEBSITE

MOBY-DIC: Model-based synthesis of digital electronic circuits for embedded control (EC-IST-VIIPM no.-248858)

PI: Antonio J. Acosta Jiménez

Funding Body: 7th Framework Programme, European Commission

Dec 2009 - Nov 2013

CRIPTO-BIO: Microelectronic design for crypto-biometric authentication (P08-TIC-03674)

PI: Iluminada Baturone Castillo

Funding Body: Junta de Andalucía - Proyectos de Excelencia

Jan 2009 - Dec 2013

WEBSITE