Analog Signal Processing

The general objective of this research line is to develop new modeling, design and synthesis strategies for analog, mixed-signal, radio-frequency (RF) and heterogeneous integrated circuits and systems, aiming at better performances, smaller design and fabrication cost and smaller power consumption. This also involves dealing with the increasing variability of modern technologies.

More specifically, the work include activities in different aspects of the circuit design flow, as well as their exploitation in industrial-class designs:

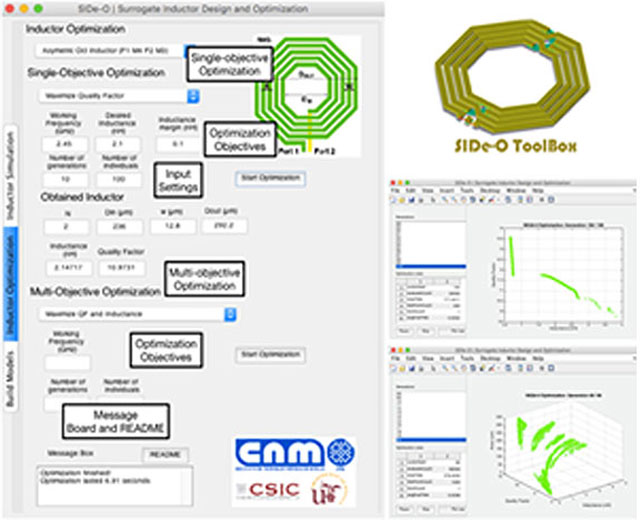

F. Passos, E. Roca, J. Sieiro, R. Castro-Lopez and F.V. Fernandez, "An Efficient Transformer Modeling Approach for mm-Wave Circuit Design", AEU - International Journal of Electronics and Communications, vol. 128, article 153496, 2021 » doi

F. Passos, E. Roca, R. Martins, N. Lourenço, S. Ahyoune, J. Sieiro, R. Castro-Lopez, N. Horta and F. V. Fernandez, "Ready-to-Fabricate RF Circuit Synthesis using a Layout- and Variability-Aware Optimization-based Methodology", IEEE Access, vol. 8, pp. 51601-51609, 2020 » doi

F. Passos, E. Roca, J. Sieiro, R. Fiorelli, R. Castro-Lopez, J.M. López-Villegas and F.V. Fernandez, "A multilevel bottom-up optimization methodology for the automated synthesis of RF system", IEEE Trans. on Computer Aided Design of Integrated Circuits and Systems, vol. 39, no. 3, pp. 560-571, 2020 » doi

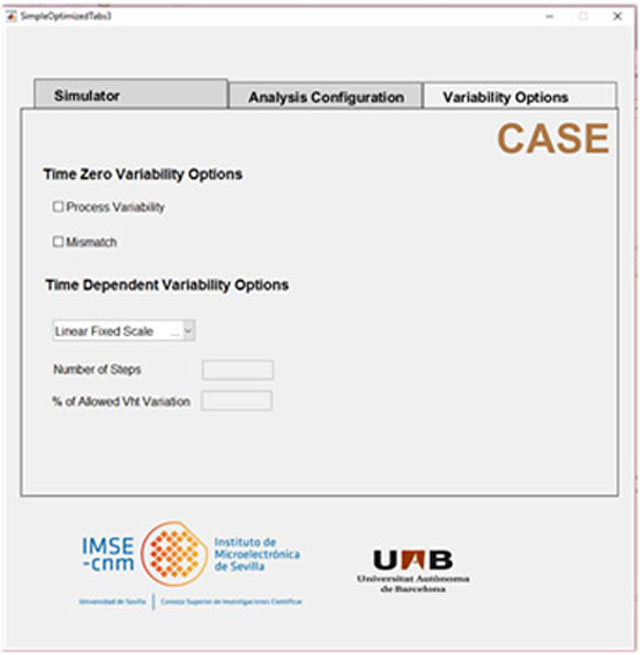

A. Toro-Frías, P. Martín-Lloret, J. Martin-Martinez, R. Castro-López, E. Roca, R. Rodriguez, M. Nafria and F.V. Fernández, "Reliability simulation for analog ICs: Goals, solutions, and challenges", Integration - the VLSI Journal, vol. 55, pp. 341-348, 2016 » doi

R. Castro-Lopez, O. Guerra, E. Roca and F.V. Fernandez, "An Integrated Layout-Synthesis Approach for Analog ICs", IEEE Trans. on Computer-Aided Design, vol. 27, no. 7, pp. 1179-1189, 2008 » doi

VIGILANT: The Variability Challenge in Nano-CMOS - SUBPROJECT MITIGATION (PID2019-103869RB-C31)

PI: Francisco V. Fernández Fernández / Rafael Castro López

Funding Body: Min. de Ciencia, Innovación y Universidades

Jun 2020 - May 2023

TOGETHER: Towards Trusted Low-Power Things: Devices, Circuits and Architectures (TEC2016-75151-C3-3-R)

PI: Francisco V. Fernández Fernández / Rafael Castro López

Funding Body: Min. de Economía, Industria y Competitividad

Jan 2017 - Jun 2021

KIT-LTCC: Design Kit Development in LTCC ceramic technology: modeling, simulation and fabrication of components and circuits, and design methodology (RTC-2014-2426-7)

PI: Elisenda Roca

Funding Body: Min. de Economía y Competitividad

Sep 2014 - Jan 2017

MARAGDA: Multilevel approach to the reliability-aware design of analog and digital integrated circuits (TEC2013-45638-C3-3-R)

PI: Francisco V. Fernández Fernández

Funding Body: Min. de Economía y Competitividad

2014 - 2018

WEBSITE

AMADEUS: Analog Modeling and Design Using a Symbolic Environment (ESPRIT IV 21821)

PI: Francisco V. Fernández Fernández

1996 - 2000