Hardware Security

This research line focuses on microelectronic solutions for security applications. The objectives are to verify the identity of hardware devices and users as well as to store and communicate sensitive information, resorting to the use of techniques from cryptography, biometrics, and their combination (crypto-biometrics). Security against hardware attacks is especially analyzed, particularly fault injection and side-channel attacks such as differential power analysis (DPA) and differential electromagnetic attacks (DEMA). Microelectronic solutions are aimed at constructions and algorithms providing security together with efficient features of size, power consumption and operation speed.

The activities within this research line are devoted to:

A. Cabrera-Aldaya, A.J. Cabrera and S. Sánchez-Solano, "SPA Vulnerabilities of the Binary Extended Euclidean Algorithm", Journal of Cryptographic Engineering, vol 7, no. 4, pp. 273285, 2017 » doi

J.M. Mora-Gutiérrez, C.J. Jiménez-Fernández and M. Valencia-Barrero, "Trivium Hardware Implementations for Power Reduction", International Journal of Circuit Theory and Applications, Special Issue: Secure lightweight crypto-hardware, vol. 45, no. 2, pp. 188-198, 2017 » doi

I. Baturone, M.A. Prada-Delgado and S. Eiroa, "Improved generation of identifiers, secret keys, and random numbers from SRAMs", IEEE Transactions on Information Forensics and Security, vol. 10, no. 12, pp. 2653-2668, 2015 » doi

E. Tena-Sánchez, J. Castro and A.J. Acosta , "A Methodology for Optimized Design of Secure Differential Logic Gates for DPA Resistant Circuits", IEEE Journal on Emerging and Selected Topics in Circuits and Systems, vol. 4, no. 2, pp 203-215, 2014 » doi

R. Arjona and I. Baturone, "A Hardware Solution for Real-Time Intelligent Fingerprint Acquisition", Journal of Real-Time Image Processing, vol. 9, no. 1, pp. 95-109, 2014 » doi

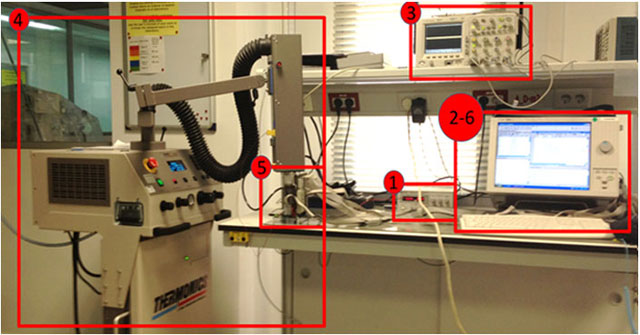

INTERVALO: Integración y validación en laboratorio de contramedidas frente a ataques laterales en criptocircuitos microelectrónicos (TEC2016-80549-R)

PI: Antonio J. Acosta Jiménez / Carlos J. Jiménez Fernández

Funding Body: Min. de Economía y Competitividad

Dec 2016 - Dec 2019

SENIAC: Security in interconnected devices by injection of authentication and ciphering algorithms (RTC-2014-2932-8)

PI: Iluminada Baturone Castillo

Funding Body: Min. de Economía y Competitividad

Oct 2014 - Mar 2017

WEBSITE

CESAR: Secure microelectronic circuits against side-channel attacks (TEC2013-45523-R)

PI: Antonio J. Acosta Jiménez / Carlos J. Jiménez Fernández

Funding Body: Min. de Economía y Competitividad

Jan 2014 - Dec 2016

WEBSITE

CB-DOC: Content management system with secure authentication by cripto-biometric techniques based on hardware (IPT-2012-0695-390000)

PI: Iluminada Baturone Castillo

Funding Body: Min. de Economía y Competitividad · Proyecto INNPACTO

Jul 2012 - Mar 2015

WEBSITE

CRIPTO-BIO: Microelectronic design for crypto-biometric authentication (P08-TIC-03674)

PI: Iluminada Baturone Castillo

Funding Body: Junta de Andalucía - Proyectos de Excelencia

Jan 2009 - Dec 2013

WEBSITE