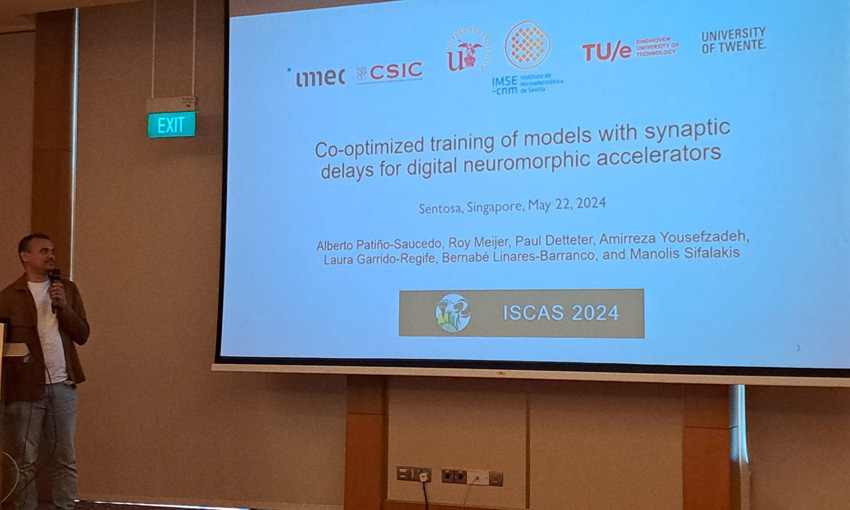

Alberto Patiño Saucedo, investigador postdoctoral del Instituto de Microelectronica de Sevilla (IMSE-CNM), ha sido galardonado al mejor paper por el Neural Systems and Applications Technical Comitee del IEEE Circuits and Systems Society (CAS). Se presentó en el Congreso ISCAS de este año, en Singapur.

El artículo lleva el título Co-optimized training of models with synaptic delays for digital neuromorphic accelerators. Se trata de un nuevo método para entrenar y desplegar redes neuronales spiking (SNNs) en hardware neuromórfico digital (es decir, que imita el funcionamiento del cerebro humano).

Este avance no solo optimiza los pesos sinápticos, sino también los retrasos sinápticos, logrando así un mejor desempeño, ya que permite desplegar modelos de inteligencia artificial de manera mucho más eficiente, reduciendo el consumo de memoria y de energía por operación sináptica. Siendo un caso de computación en el borde (edge computing), abre la puerta a tecnologías más avanzadas rápidas y seguras, y podría tener aplicaciones en campos como la medicina, la robótica y la tecnología de consumo.

Desde el Instituto de Microelectrónica de Sevilla queremos darle la enhorabuena por este premio internacional.

Puedes ampliar la información del paper en el siguiente enlace.

Instituto de Microelectrónica de Sevilla

10 Junio 2024