# SIMSIDES User Guide

José M. de la Rosa

Institute of Microelectronics of Seville, IMSE-CNM (CSIC/University of Seville) jrosa@imse-cnm.csic.es

September 2018

# **CONTENTS**

| I | SIM  | SIDES                                                 | User Guide                                                        | 1  |

|---|------|-------------------------------------------------------|-------------------------------------------------------------------|----|

|   | 1.1  | Gettin                                                | g Started: Installing and Running SIMSIDES                        | 1  |

|   | 1.2  | Buildi                                                | ng and Editing $\Sigma\Delta M$ Architectures in SIMSIDES         | 2  |

|   | 1.3  | Analy                                                 | zing $\Sigma\Delta Ms$ in SIMSIDES                                | 2  |

|   | 1.4  | Optim                                                 | ization Interface                                                 | 13 |

|   | 1.5  | Tutori                                                | al Example: Using SIMSIDES to Model and Analyze $\Sigma\Delta Ms$ | 15 |

|   | 1.6  | Gettin                                                | g Help                                                            | 23 |

|   | Refe | erences                                               |                                                                   | 23 |

| 2 | SIM  | SIDES                                                 | Block Libraries and Models                                        | 25 |

|   | 2.1  | Overv                                                 | iew of SIMSIDES Libraries                                         | 25 |

|   | 2.2  | Ideal l                                               | Libraries                                                         | 25 |

|   |      | 2.2.1                                                 | Ideal Integrators                                                 | 25 |

|   |      | 2.2.2                                                 | Ideal Resonators                                                  | 27 |

|   |      | 2.2.3                                                 | Ideal Quantizers                                                  | 28 |

|   |      | 2.2.4                                                 | Ideal D/A Converters                                              | 30 |

|   | 2.3  | Real S                                                | SC Building-Block Libraries                                       | 31 |

|   |      |                                                       | Real SC Integrators                                               | 31 |

|   |      | 2.3.2                                                 | Real SC Resonators                                                | 33 |

|   | 2.4  |                                                       | SI Building-Block Libraries                                       | 33 |

|   |      | 2.4.1                                                 | Real SI Integrators                                               | 33 |

|   |      | 2.4.2                                                 | Real SI Resonators                                                | 36 |

|   |      | 2.4.3                                                 | SI Errors and Model Parameters                                    | 37 |

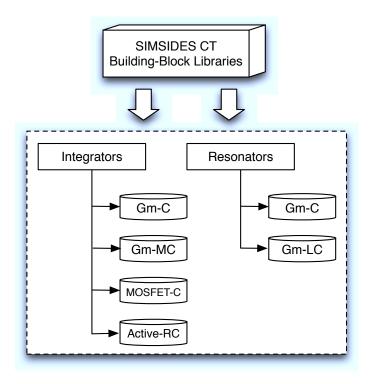

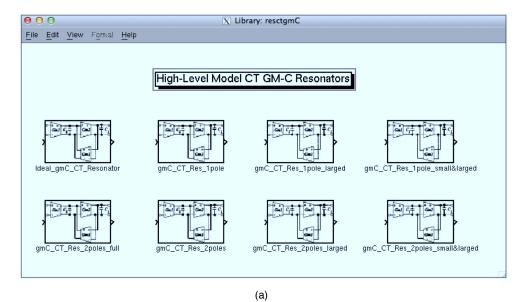

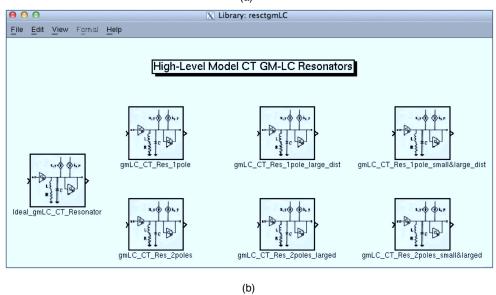

|   | 2.5  |                                                       | CT Building-Block Libraries                                       | 41 |

|   |      | 2.5.1                                                 | Real CT Integrators                                               | 41 |

|   |      | 2.5.2                                                 | Trous of Tropoliurors                                             | 49 |

|   | 2.6  | Real (                                                | Quantizers & Comparators                                          | 52 |

|   | 2.7  | Real I                                                | D/A Converters                                                    | 53 |

|   | 2.8  | Auxiliary Blocks                                      |                                                                   | 54 |

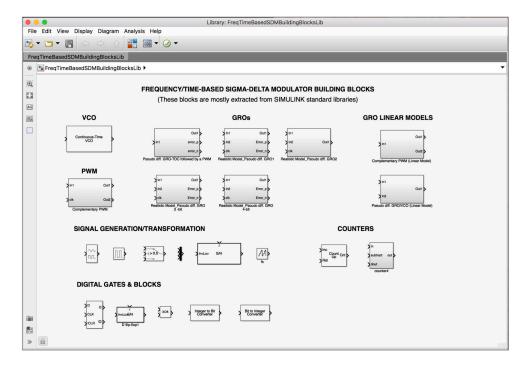

|   | 2.9  | Frequency/Time-based $\Sigma\Delta M$ Building Blocks |                                                                   | 55 |

|   | Refe | erences                                               |                                                                   | 56 |

# 1

# SIMSIDES User Guide

SIMSIDES (SIMulink-based SIgma-DElta Simulator) is a time-domain behavioral simulator for  $\Sigma\Delta Ms$  that has been developed as a toolbox in the MATLAB/SIMULINK environment. SIMSIDES can be used for simulating any arbitrary  $\Sigma\Delta M$  architecture, implemented with both discrete-time and continuous-time circuit techniques. To this end, a complete list of  $\Sigma\Delta M$  building blocks (integrators, resonators, quantizers, embedded DACs, etc) is included in the toolboox. The behavioral models of these building blocks take into account the most critical error mechanisms of different circuit techniques including SC, SI, and CT circuits. These models, validated through transistor-level electrical simulations and by experimental measurements taken from a number of silicon prototypes, have been incorporated into the SIMULINK environment as C-MEX S-functions. This approach drastically increases the computational efficiency in terms of CPU time and accuracy of the simulation results.

The behavioral models included in SIMSIDES have been compiled and tested in a number of operating systems, including Mac OS X, UNIX (Solaris), Linux, and Microsoft Windows. Both 32-bit and 64-bit system platforms have been successfully tested in the majority of them. Although SIMSIDES was originally developed using version 6.5 of MATLAB, the toolbox has been updated and successfully used in a number of MATLAB/SIMULINK versions over the last years.

This document provides a user guide of SIMSIDES, giving an overview of the most significant features of the simulator. The interested reader can find more details in related publications [1,2].

# 1.1 Getting Started: Installing and Running SIMSIDES

A free copy of SIMSIDES can be downloaded from the following web site:

http://www.imse-cnm.csic.es/simsides

This website contains also this user guide, examples and a link to a YouTube demo video about SIMSIDES.

After completing the online registration form and accepting the terms and conditions for using SIMSIDES, a zip file named simsides.zip is downloaded. The following steps must be followed to install the toolbox:

- 1. Uncompress the simsides.zip file to a directory of your computer hard disk. Let us assume that the directory is named SIMSIDES.

- 2. Start MATLAB.

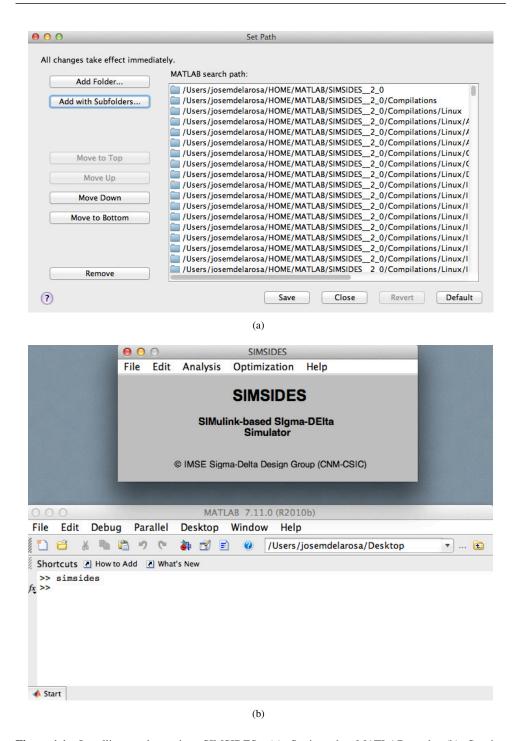

3. Set the MATLAB search path in order to add the SIMSIDES directory. To do this, go to File menu in MATLAB and select Set Path. The Set Path dialog box opens, listing all folders on the search path. From this dialog box, click the button Add with Subfolders and select the SIMSIDES directory to add to the search path. In order to reuse the newly modified search path including SIMSIDES directory and subdirectories, click Save, and finally click Close. This procedure—illustrated in Figure 1.1a—must be done only the first time SIMSIDES is installed in your hard disk.

In order to start SIMSIDES, type simsides at the MATLAB prompt and the SIMSIDES main window is displayed, as illustrated in Figure 1.1b.

# 1.2 Building and Editing $\Sigma \Delta M$ Architectures in SIMSIDES

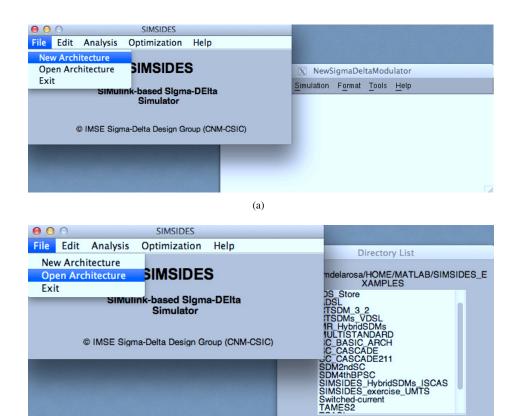

To create a new  $\Sigma\Delta M$  architecture in SIMSIDES, select File and then New Architecture in the main menu, and a new SIMULINK model window is displayed. Alternatively, an existing  $\Sigma\Delta M$  architecture can be opened by selecting File -> Open Architecture as illustrated in Figure 1.2.

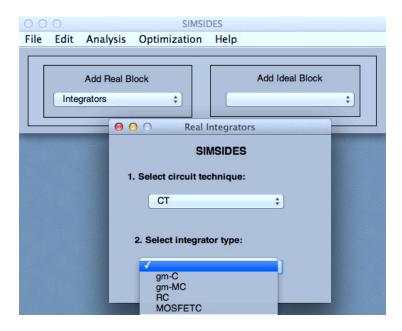

In order to define a  $\Sigma\Delta M$  block diagram in SIMSIDES, the required building blocks can be incorporated from the Edit menu as shown in Figure 1.3. Both SIMULINK and SIMSIDES library models can be included by selecting Edit -> SIMULINK Library or Edit -> Add block, respectively. The latter option allows users to browse through all SIMSIDES library models. This way, clicking on Edit -> Add blocks new window is displayed where the user can select either ideal or real building blocks, by choosing either Add Ideal Block or Add Real Block menus, respectively. In both cases, building-block models are organized in a set of sublibraries, namely: integrators, quantizers & comparators, D/A converters, resonators, and auxiliary blocks. The latter are only available in real libraries.

Some model libraries are grouped in sublibraries that contain different models corresponding to different kinds of circuit implementations. For instance, if library Real Integrators is selected, a new window is displayed where the user can select the circuit technique (CT, SC, or SI) as well as the type of integrator (i.e., either FE or LD in the case of SC and SI integrators, and Gm-C, Gm-MC, active-RC, MOSFET-C in the case of CT integrators). As an illustration, Figure 1.3 shows different sublibraries contained in the Real Integrators library. A complete list of model libraries and sublibraries is given in Chapter 2 of this user guide.

Once the  $\Sigma\Delta M$  block diagram is completed and the different building-block model parameters have been defined in the MATLAB workspace, the modulator can be simulated in SIMULINK following the same procedure as for the simulation of an arbitrary model in SIMULINK; i.e., choosing Simulation -> Start menu in the SIMULINK model window.

# 1.3 Analyzing $\Sigma \Delta Ms$ in SIMSIDES

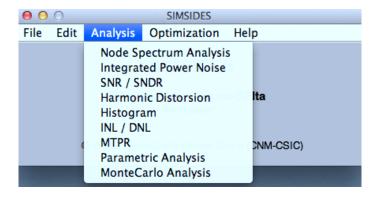

Simulation output data can be post-processed in SIMULINK using the Analysis menu. As illustrated in Figure 1.4, the Analysis menu includes the following submenus:

Node Spectrum Analysis, which computes and plots the FFT magnitude spectrum of a given signal.

**Figure 1.1** Installing and starting SIMSIDES: (a) Setting the MATLAB path. (b) Starting SIMSIDES at the MATLAB prompt (see also the demo video available in YouTube at https://www.youtube.com/watch?v=zT5XhBqysgU).

**Figure 1.2** Building and editing  $\Sigma\Delta Ms$  in SIMSIDES: (a) Creating a new  $\Sigma\Delta M$  architecture. (b) Opening an existing model.

(b)

- Integrated Power Noise, used for calculating and graphically representing the IBN within a given signal bandwidth.

- SNR/SNDR , which computes the SNR and/or SNDR within the band of interest, considering both LP- and BP- $\Sigma\Delta$ Ms.

- Harmonic Distortion, that computes dynamic harmonic distortion figures, like THD and intermodulation distortion figures.

- $\bullet$  Histogram, used for representing histograms and analyzing the input/output swing in  $\Sigma\Delta M$  building blocks.

- INL/DNL, which calculates static harmonic distortion.

- MTPR, used for computing multi-tone power ratio (MTPR).

- $\bullet$  Parametric Analysis , which allows to simulate the impact of a given model parameter on the performance of  $\Sigma\Delta Ms.$

- Monte Carlo Analysis, to do Monte Carlo simulations.

Figure 1.3 Illustrating different sublibraries included in the Real Integrators library.

Figure 1.4 Analysis menu in SIMSIDES.

The required parameters and details involving the aforementioned analysis menus are described below.

# **Node Spectrum Analysis**

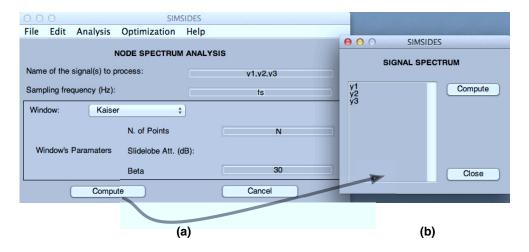

Figure 1.5a shows the SIMSIDES Node Spectrum Analysis window. The following parameters are required to compute the FFT magnitude spectrum:

- Name of the signal(s) to process, where different variable names can be introduced, separated by commas. These variables can be output data generated in the simulations (for instance, the modulator output data stream), which have been previously saved in the MATLAB workspace by using the To Workspace SIMULINK block.

- Sampling frequency; i.e., the sampling frequency in Hz.

- Window, which defines the window function used for computing the FFT. The main window functions available in MATLAB can be selected, namely: Kaiser, Barlett, Blackman, Hamming, Hanning, Chebyshev, Boxcar, and Triangular.

- Number of Points; i.e., the number of points (N in Figure 1.5) for the selected window function and for FFT computation.

- Window Parameters, where other parameters required to define the window function are defined (like Beta parameter used in Kaiser windows).

Once these parameters have been defined, the output spectrum can be computed by clicking on the Compute button and then selecting the signal to be processed from the new window that is displayed (Signal Spectrum window shown in Figure 1.5b).

**Figure 1.5** Node spectrum analysis menu.

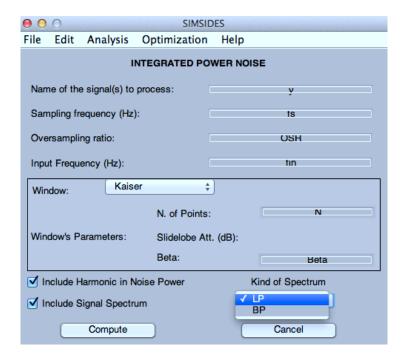

Figure 1.6 Integrated power noise menu.

# **Integrated Power Noise**

Figure 1.6 shows the SIMSIDES Integrated Power Node window used for computing the IBN of any arbitrary data sequence obtained from simulations. To compute IBN, the following parameters are required:

- Name of the signal(s) to process.

- Sampling frequency; i.e., the sampling frequency in Hz.

- Oversampling ratio; i.e., the value of OSR that defines the signal bandwidth in which the IBN is computed.

- Input frequency, where it is assumed that a single-tone input signal is applied.

- Window Parameters; i.e., the parameters required to defined the window function used for computing the IBN.

- Kind of Spectrum, which specifies the signal nature; i.e., low-pass (LP) or bandpass (BP).

After defining all parameters described above, the IBN is computed by clicking on the Compute button. Harmonic distortion can be also taken into account in the calculation of the IBN by clicking the Include Harmonic in Noise Power button. The signal spectrum can be also plotted together with the IBN by choosing the Include Signal Spectrum option.

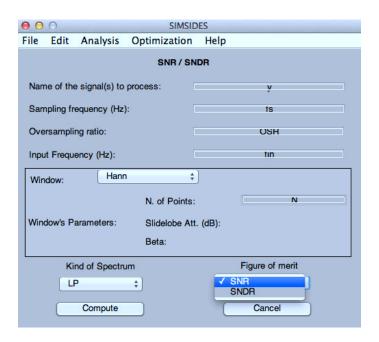

# SNR/SNDR

Figure 1.7 shows the SIMSIDES SNR/SNDR window. The parameters required to calculate the SNR/SNDR of a given signal are essentially the same as those used for computing IBN—described in the previous section. In this case either the SNR or the SNDR is computed depending on the Figure of merit selected. Note that this kind of analysis calculates the SNR/SNDR for a given value of the input signal amplitude. If a SNR-versus-amplitude curve is required, a parametric analysis should be chosen as will be described later.

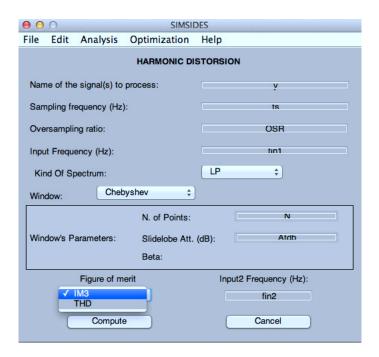

# **Harmonic Distortion**

Figure 1.8 shows the SIMSIDES Harmonic Distortion window, which is used for computing the harmonic distortion power. Two different figures of merit can be calculated, namely: THD and third-order intermodulation distortion (IM3 in Figure 1.8). The latter requires using a two-tone input signal. For that reason, there is an additional parameter named Input2 Frequency that defines the frequency of the second input tone.

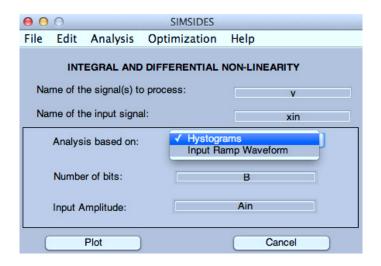

# **Integral and Differential Non-Linearity**

The INTEGRAL AND DIFFERENTIAL NON-LINEARITY menu, illustrated in Figure 1.9, is used for characterizing the static linearity in SIMSIDES. The analysis is based on either Histograms or Input Ramp Waveform—selected by the user. Other parameters required

Figure 1.7 SNR/SNDR menu.

Figure 1.8 Harmonic distortion analysis menu.

to do this analysis are the Input Amplitude and the Number of bits, which specifies the ideal resolution of the A/D conversion, expressed in bits.

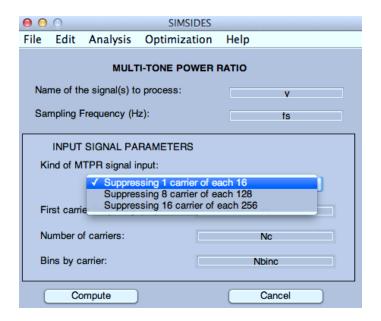

# **Multi-Tone Power Ratio**

SIMSIDES can also analyze the harmonic distortion in some communication applications where a discrete multi-tone (DMT) signal is used. In this case, the linearity of the system is measured by a figure named multi-tone power ratio (MTPR). The corresponding SIMSIDES menu–shown in Figure 1.10–allows to compute MTPR for DMT input signals of different types:

- Supressing 1 carrier of each 16; i.e., 1 out of 16 carrier channels are suppressed.

- Supressing 8 carrier of each 128; i.e., 8 out of 128 carrier channels are suppressed.

- Supressing 16 carrier of each 256; i.e., 16 out of 256 carrier channels are suppressed.

In addition, the following parameters are also needed to compute MTPR:

• Number of carriers, which stands for the number of carrier channels in which the DMT signal is divided.

Figure 1.9 Integral and differential non-linearity analysis menu.

• Bins by carrier; the number of bins assigned to each carrier channel in the FFT.

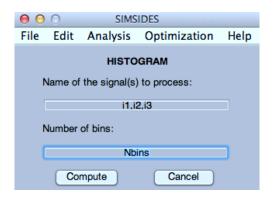

# Histogram

Histograms of signals that have been previously saved on the MATLAB workspace can be computed using the <code>HISTOGRAM</code> menu (illustrated in Figure 1.11), where the <code>Number of bins</code> specifies the number of intervals in which the signal range will be divided to compute the histogram.

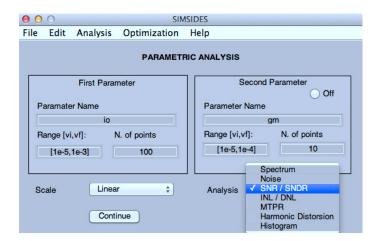

# **Parametric Analysis**

Figure 1.12 shows the SIMSIDES PARAMETRIC ANALYSIS menu. This menu is used for analyzing the impact of varying a model parameter on the performance of  $\Sigma\Delta Ms$ . Either one parameter or two parameters can be varied simultaneously by selecting the Second Parameter option. For each parameter, the following data must be specified:

- Parameter Name; i.e., the name of the model parameter to be varied. This model parameter can be a variable used in a  $\Sigma\Delta M$  building block model (like for instance  $I_o$ ,  $g_m$ , etc) or a simulation parameter, like the input signal amplitude, sampling frequency, etc.

- Range [vi,vf], which defines the variation range, defined by an interval with a lower value given by vi and a upper value of vf.

- N. of points; i.e., the number of points in which the variation interval is divided.

- Scale, that specifies if the variation range is either linear or logarithmic.

- Analysis, that specifies the type of analysis to be carried out, including output spectrum, IBN, SNR/SNDR, INL, MTPR, harmonic distortion, histograms, etc.

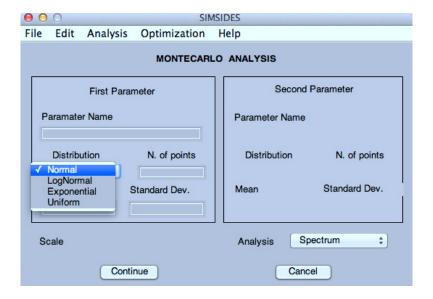

# Monte Carlo Analysis

Figure 1.13 shows the SIMSIDES menu to run a Monte Carlo analysis. This is a particular case of parametric analysis, which has essentially the same functionalities and model parameters. The only difference is that the variation of the parameters involved in the Monte Carlo analysis are randomly varied according to a probability distribution with a mean value and a standard deviation which are specified in the analysis menu. Different types of probability distributions can be chosen, including Normal, Log-Normal, Exponential, and Uniform distributions.

Figure 1.10 Multi-tone power ratio analysis menu.

Figure 1.11 Histogram analysis menu.

Figure 1.12 Parametric analysis menu.

Figure 1.13 Monte Carlo analysis menu.

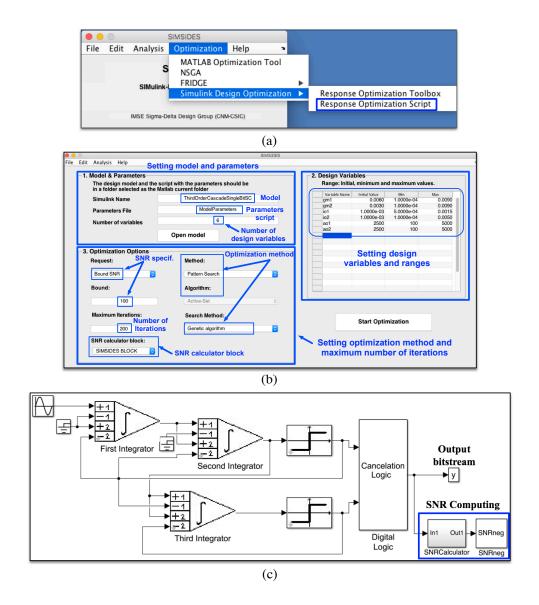

# 1.4 Optimization Interface

SIMSIDES includes an optimization interface to assist designers to combine time-domain behavioral simulation with optimization in order to automate and systematize the high-level design of  $\Sigma\Delta Ms$  [3]. Figure 1.14a shows a snapshot of the optimization menu. A number of solvers such as Fmincon , Fminsearch , Patternsearch , search

**Figure 1.14** SIMSIDES optimization menu. (a) Main window. (b) GUI for setting optimization. (c) Model including the additional block to compute SNR while running optimization.

methods like <code>Gradient Descent</code>, <code>Simplex Search</code>, <code>Pattern</code>, etc. as well as diverse optimization algorithms, namely: <code>Neider-Mead</code>, <code>Genetic</code>, etc. can be used. In addition, some optimization engines—such as Multi-Objective Evolutionary Algorithm (MOEAs) like NSGA-II—is also included.

The SIMULINK Design Optimization toolbox can be used with any arbitrary SIMULINK model, and hence, SIMSIDES models can be also combined with this toolbox. However, although a powerful and user friendly GUI is provided, the formulation of the optimization problem is not an easy task when applied to the design of ADCs, and particularly to  $\Sigma\Delta$ Ms. The reason is that a suitable performance metric—like for instance the SNR—cannot be directly set from the optimization toolbox, which is mostly focused on optimizing the frequency response of filters based on fine tuning their Bode diagrams.

In order to address these problems, a dedicated interface has been developed and embedded in SIMSIDES in order to help designers combine the benefits of its time-domain behavioral models for  $\Sigma\Delta Ms$  with the different optimization methods and algorithms available in MATLAB. Figure 1.14b illustrates an excerpt of the SIMSIDES optimization interface. This optimization menu allows designers to customize their optimization problem by setting all required pieces of information, namely: name of the SIMSIDES model, MATLAB script including main simulation parameters, number of design variables, initial values and ranges of variables and the optimization method. To this end, designers need to follow these three basic steps:

- Build a model of the  $\Sigma \Delta M$  in SIMSIDES

- Create a MATLAB script with all design variables to be optimized as well as the parameters required to simulate the  $\Sigma\Delta M$  model

- Enter the information corresponding to the SIMSIDES model and the MATLAB script in the SIMSIDES optimization interface.

Different performance metrics can be used for optimization purposes. Without loss of generality, the SNR has been considered. Therefore, the design objective is to maximize the SNR while optimizing the  $\Sigma\Delta M$  building-block design variables in order to minimize the power consumption. However, the optimization solvers and algorithms available in MATLAB are intended to minimize a given function, rather than to maximize it – as it is the case here. Therefore, in order to overcome this limitation, an additional block is added to the SIMSIDES model–depicted in Figure 1.14c– which calculates the SNR at the output of the  $\Sigma\Delta M$  output bitstream and obtains the negative value of the computed SNR, so that the optimization problem can be formulated as:

$$\text{maximize } [f(\bar{x})] = \text{minimize } [-f(\bar{x})] \tag{1.1}$$

where  $f(\bar{x})$  is the performance metric to be optimized–SNR in this case–and  $\bar{x}$  denotes the vector of design variables involved in the optimization, i.e. the  $\Sigma\Delta M$  building-block specifications to be minimized/maximized in order to get the maximum SNR with the minimum power consumption. For the design variables, initial values and ranges need to be entered as depicted in Figure 1.14b. Also, the algorithm solver and search method used in the optimization are set as well as the maximum number of iterations to be considered in order to limit the CPU time in case the synthesis process does not converge to any solution. During the optimization procedure, the toolbox gives information about both the number

of iterations and the number of simulations. The former refers to the number of times the optimization algorithm is run whereas the later stands for the number of time the  $\Sigma\Delta M$  is simulated. The interested reader can find more detailed information about the combined used of SIMSIDES with MATLAB optimizers in [3].

# 1.5 Tutorial Example: Using SIMSIDES to Model and Analyze $\Sigma \Delta Ms$

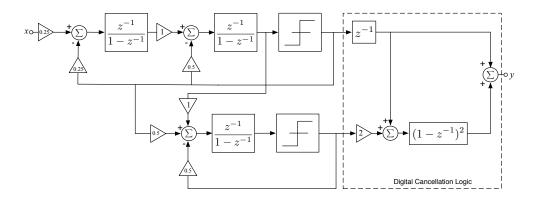

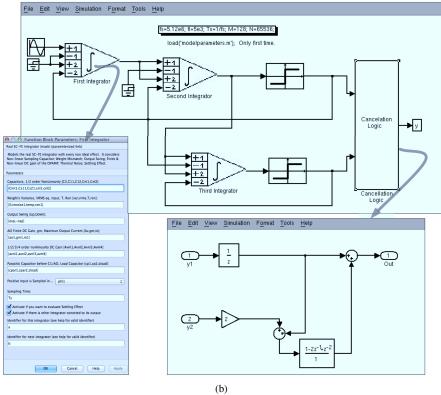

This section illustrates the use of SIMSIDES through a simple example in which several kinds of analysis will be carried out to show the main features of the simulator<sup>1</sup>. Figure 1.15 shows the block diagram of the modulator under study, which consists of a third-order cascade 2-1 DT- $\Sigma\Delta M$  with single-bit quantization in both stages.

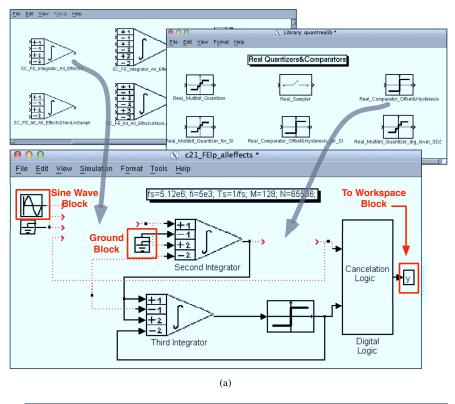

# Creating the Cascade 2-1 $\Sigma\Delta M$ Block Diagram in SIMSIDES

The modulator block diagram shown in Figure 1.15 can be implemented by using the model libraries available in SIMSIDES. To this end, the same procedure as described in Section 1.2 is followed:

- ullet Go to SIMSIDES main menu, select File -> New Architecture and introduce a name for the new  $\Sigma\Delta M$  architecture.

- Include the integrators and comparators from the SIMSIDES model libraries. To do this, select Edit -> Add Block. In this example, the FE integrators in Figure 1.15 are implemented by using the SC\_FE\_Integrator\_All\_Effects blocks from the Real Integrators library, whereas single-bit quantizers are modeled by the Real\_Comparator\_Offset&Hysteresis comparator block available in Quantizers&Comparators library. These building blocks can be incorporated in the new architecture by simply dragging and dropping the models from their corresponding SIMSIDES libraries, as illustrated in Figure 1.16a.

<sup>&</sup>lt;sup>1</sup>The interested reader can find more examples and details in [2].

**Figure 1.15** Z-domain block diagram of a cascade 2-1 DT- $\Sigma\Delta M$ .

**Figure 1.16** SIMSIDES block diagram of the  $\Sigma\Delta M$  shown in Figure 1.15: (a) Building and editing the block diagram. (b) Complete modulator block diagram in SIMSIDES.

- Incorporate the remaining building blocks from the SIMULINK model library. To do this, go to Edit -> Simulink Library and drag the required models. In this example the following blocks are required: Sine Wave and Ground blocks from Sources library, Unit Delay and Discrete Filter block from the Discrete library, and To Workspace from Sinks library.

- Finally, once all required blocks have been included in the new architecture, they are properly connected to implement the required  $\Sigma\Delta M$  architecture shown in Figure 1.16b.

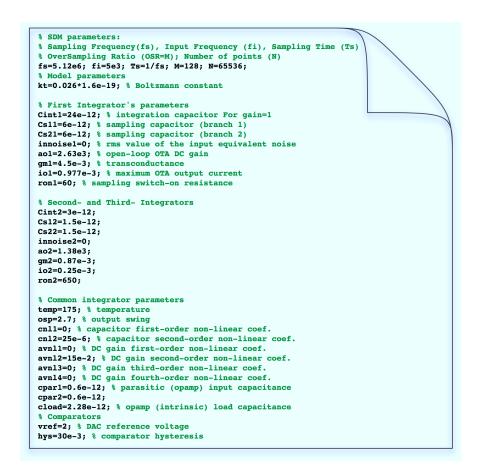

# **Setting Model Parameters**

The modulator parameters and model parameters required to simulate the block diagram of Figure 1.16 can be either set up in the MATLAB command window or they can be alternatively saved in an M-file that is loaded when needed. As an illustration, Figure 1.17 shows the M-file used for setting up all model parameters of Figure 1.16, that also includes a brief description of the different parameters and variables included. For the sake of completeness, Table 1.1 includes the values of all building-block parameters as they are described in the SIMSIDES user masks, as well as other auxiliary block parameters (such as those used in Sine Wave and To Workspace blocks) which are required during simulation. In addition to these model parameters, simulation parameters must be set up to run a simulation. To do this, go to Simulation -> Simulation Parameters menu and define the following parameters:

- Simulation Time: Start Time: 0.0; Stop Time: (N-1) \*Ts

- Solver options: Type: Variable Step; Max Step Size: Auto

Note that integrator building blocks are identified in order to properly compute the equivalent load capacitances required for the incomplete settling error model.

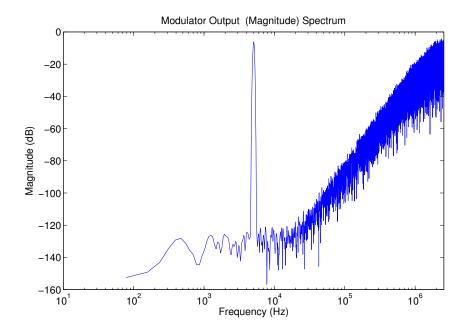

# **Computing the Output Spectrum**

The output spectrum of the  $\Sigma\Delta M$  can be computed in SIMSIDES by following the next steps:

- Set up model parameters by using the M-file shown in Figure 1.17.

- Simulate the modulator in Figure 1.16b from the menu Simulation -> Start.

- Once the simulation has finished, go to Analysis -> Node Spectrum Analysis menu in SIMSIDES.

- Define the parameters requested in that menu. In this example, the sampling frequency is defined as fs and a Kaiser window function is used with a number of points N and Beta = 20.

- Click on Compute and then Plot, and the output spectrum shown in Figure 1.18 is displayed.

$\textbf{Table 1.1} \quad \text{Building-block model parameters used for simulating the } \Sigma\Delta \text{M in Figure 1.16b}.$

| <b>Building Block</b>        | Parameter Description                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Value/Variable                                                                                                                |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Input Sine Wave              | Sine Type Amplitude Bias Frequency (rad/s) Phase (rad) Sample time Interpret vector parameters                                                                                                                                                                                                                                                                                                                                                                             | Time based 0.5 0 2*pi*fi 0 Selected                                                                                           |

| First Integrator             | Integration and Sampling Capacitors (Branch 1, Branch 2) Capacitor nonlinear coefficients Weight's variance, rms eq.input noise, temperature OTA DC gain, transconductance, max. output current Positive/Negative Output swing Switch on-resistance OTA DC gain nonlinear coefs. Parasitic capacitances before the OTA Load capacitance Positive Input 1 is sampled at Sampling Time Identifier for this integrator Identifier for the next integrator                     | [Cint1,Cs11,Cs21] [cnl1,cnl2] [0,innoise1,temp] [ao1,gm1,io1] [osp,-osp] ron1 [avnl1,2,3,4] [cpar1,cpar2] cload phi1 Ts a b   |

| Second, Third<br>Integrators | Integration and Sampling Capacitors (Branch 1, Branch 2) Capacitor nonlinear coefficients Weight's variance, rms eq.input noise, temperature OTA DC gain, transconductance, max. output current Positive/Negative Output swing Switch on-resistance OTA DC gain nonlinear coefs. Parasitic capacitances before the OTA Load capacitance Positive Input 1 is sampled at Sampling Time Identifier for this integrator (second integrator) Identifier for the next integrator | [Cint2,Cs12,Cs22] [cnl1,cnl2] [0,innoise2,temp] [ao2,gm2,io2] [osp,-osp] ron2 [avnl1,2,3,4] [cpar1,cpar2] cload phi1 Ts b c c |

| Comparators                  | Vhigh, Vlow Offset, Hysteresis Phase ON Sampling Time Identifier for this quantizer                                                                                                                                                                                                                                                                                                                                                                                        | [vref, -vref]<br>[0,hys]<br>phi1<br>Ts<br>quant1                                                                              |

| To Workspace (y)             | Variable name Limit data points to last Decimation Sample Time Save format                                                                                                                                                                                                                                                                                                                                                                                                 | y<br>N<br>1<br>Ts<br>Array                                                                                                    |

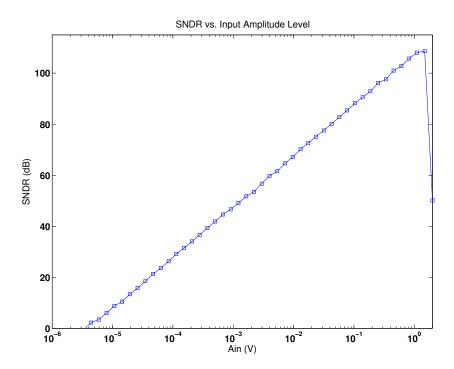

# **SNR versus Input Amplitude Level**

Figure 1.19 shows the SNDR versus input amplitude level (or SNDR curve) of the  $\Sigma\Delta M$  in Figure 1.16b. This figure has been obtained by using the Analysis menu and choosing SNR/SNDR analysis<sup>2</sup>. In this example, the following parameters are used:

- Parameter Name: Ain, where Ain is the Amplitude parameter defined in the Input Sine Wave block in Figure 1.16b.

- Range [vi, vf]: [1e-6,2]

- N. of points: 50

- Scale: Logarithmic

<sup>&</sup>lt;sup>2</sup>Alternative, a specific SNDR-vs-amplitude analysis can be carried out in which the input amplitude is represented in dB referred to the Full-Scale (FS) range (dBFS). To do so, go to *Analysis*—>*Parametric Analysis*—>*SNR/SNDR vs Amplidute (dBFS)*.

**Figure 1.17** M-file including all model parameters required to simulate the  $\Sigma\Delta M$  in Figure 1.16b.

- Analysis: SNR/SNDR

- Second Parameter: Off

Once the aforementioned parameters are set up, click on Continue and the SNR/SNDR window menu shown in Figure 1.7 is displayed. The requested parameters (i.e., sampling frequency, oversampling ratio, etc) are set up according to the values given in Figure 1.17, namely:

- Name of the signal(s) to process: y

- Sampling frequency (Hz): fs

- Oversampling ratio: M

- Input Frequency (Hz): fi

- Window: Kaiser

- N. of Points: N

- Beta: 20

- Kind of Spectrum: LP

- Figure of merit: SNDR

After setting up the aforementioned parameters, click on Compute and then Plot to obtain the curve given in Figure 1.19.

Figure 1.18 Output spectrum (magnitude) of the  $\Sigma\Delta M$  in Figure 1.16b.

# Parametric Analysis Considering Only One Parameter

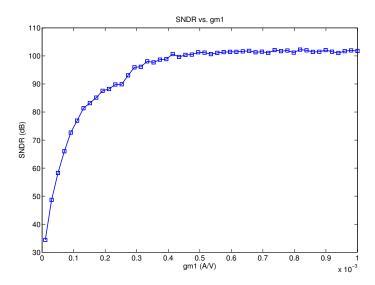

The Parametric Analysis menu can be used for studying the effect of a given model parameter on the modulator performance. For instance, let us consider the effect of the OTA transconductance  $g_m$  of the front-end integrator in Figure 1.16b. In order to analyze the impact of this parameter on the effective resolution of the modulator, go to Parametric Analysis menu and set up the following parameters:

- $\bullet$  Parameter name: gm1, which stands for  $g_m$  of the front-end integrator block in Figure 1.16b.

- Range [vi,vf]: [1e-5,1e-3]

- N. of points: 50

- Scale: Linear

- Analysis: SNR/SNDR

- Second Parameter: Off

Once these parameters are defined, click on Continue and proceed in a similar way to previous examples in order to compute the SNDR. Figure 1.20 shows the results of this analysis, by depicting the SNDR versus gm1.

**Figure 1.19** SNDR versus input amplitude level of the  $\Sigma\Delta M$  in Figure 1.16b.

**Figure 1.20** Using parametric analysis to study the effect of a single model parameter: SNDR versus transconductance of the front-end amplifier for the  $\Sigma\Delta M$  in Figure 1.16b.

# **Parametric Analysis Considering Two Parameters**

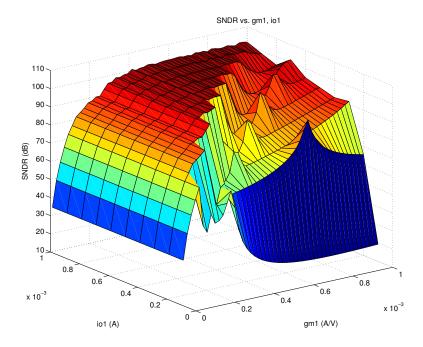

The Parametric Analysis menu can be used also for implementing parametric analyses considering the variation of two different parameters. As an example, Figure 1.21 shows the effect of both the OTA transconductance  $g_{m1}$  and the maximum output current  $I_{o1}$  of the front-end amplifier on the SNDR of the  $\Sigma\Delta M$  in Figure 1.16b.

In order to obtain the graph in Figure 1.21, the following parameters are set up in the Parametric Analysis menu:

- ullet Parameter name: io1, which stands for the maximum output current  $I_o$  of the front-end integrator.

- Range [vi,vf]: [1e-4,1e-3]

- N. of points: 10

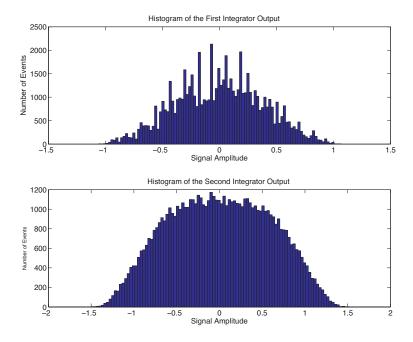

# **Computing Histograms**

Finally, to conclude this example, Figure 1.22 illustrates the histograms of the integrators outputs in the front-end stage of the modulator in Figure 1.16b.

These histograms have been obtained by using the Analysis -> Histograms menu from SIMSIDES and setting up the following model parameters:

- Name of the signal(s) to process: y1, y2, which are the names given to the output of the integrators saved into the MATLAB workspace by using To Workspace blocks from the SIMULINK elementary library.

- Number of bins: 100

# 1.6 Getting Help

SIMSIDES includes a help menu (illustrated in Figure 1.23) from which this user guide can be opened by selecting  $Help \rightarrow User Manual$  in the SIMSIDES main window. In addition, a complete list of all behavioral models (and their corresponding parameters) included in SIMSIDES—described in Chapter 2—can be also obtained from this menu by selecting  $Help \rightarrow Libraries$  and Models.

# References

- [1] J. Ruiz-Amaya et al., "High-Level Synthesis of Switched-Capacitor, Switched-Current and Continuous-Time  $\Sigma\Delta$  Modulators Using SIMULINK-based Time-Domain Behavioral Models," *IEEE Trans. on Circuits and Systems I: Regular Papers*, pp. 1795–1810, Sep. 2005.

- [2] J. M. de la Rosa, Sigma-Delta Converters: Practical Design Guide (2nd Edition). Wiley-IEEE Press, 2018.

- [3] B. Cortes-Delgadillo et al., "Embedding MATLAB Optimizers in SIMSIDES for the High-Level Design of Sigma-Delta Modulators," *IEEE Transactions on Circuits and Systems - II: Express Briefs*, vol. 65, pp. 547– 551, May 2018.

**Figure 1.21** Parametric analysis considering the effect of two parameters  $(g_{m1} \text{ and } I_{o1})$  on the SNDR.

Figure 1.22 Illustrating the use of histograms of the modulator in Figure 1.16b.

Figure 1.23 Help menu.

# SIMSIDES Block Libraries and Models

This chapter contains a compilation of most of the  $\Sigma\Delta M$  building blocks and libraries included in SIMSIDES. A brief description of their purpose and functionality, as well as their main model parameters, is provided. Revised versions of this chapter are periodically updated at SIMSIDES website and provided together with this user manual included in SIMSIDES. In addition, a list of  $\Sigma\Delta M$  models available in SIMSIDES can be downloaded from the SIMSIDES web site at: http://www2.imse-cnm.csic.es/simsides/docs/SIMSIDES\_Examples.pdf.

# 2.1 Overview of SIMSIDES Libraries

Table 2.1 compiles all libraries included in SIMSIDES together with a brief description of their contents. These libraries are divided into two main categories: ideal libraries and real libraries. The former contains ideal building blocks, whereas the latter includes behavioral models that incorporate circuit-level nonidealities. The libraries containing integrators and resonators are subdivided into several specific sublibraries, which include in turn building-block models corresponding to different circuit-level implementations. For instance, SC integrators are subdivided into FE and LD integrators; CT integrators are subdivided into Gm-C, active-RC, etc.

# 2.2 Ideal Libraries

As shown in Table 2.1, SIMSIDES includes four ideal libraries, namely: integrators, resonators, quantizers, and DACs. The building blocks contained in these libraries are described in the following sections.

# 2.2.1 Ideal Integrators

There are three kinds of ideal integrators in this library, namely: Ideal\_CT\_Integrator, Ideal\_FE\_Integrator, and Ideal\_LD\_Integrator.

| Ideal Libraries          | Sublibraries         | <b>Building Blocks</b>                    |

|--------------------------|----------------------|-------------------------------------------|

| Integrators              | -                    | Ideal DT/CT integrators                   |

| Resonators               | _                    | Ideal resonators                          |

| Quantizers & Comparators | _                    | Ideal quantizers                          |

| D/A Converters           | -                    | Ideal DACs                                |

| Real Libraries           | Sublibraries         | <b>Building Blocks</b>                    |

| Integrators              | SC FE integrators    | Forward-Euler SC integrators              |

|                          | SC LD integrators    | Lossless-Direct SC integrators            |

|                          | SI FE integrators    | Forward-Euler SI integrators              |

|                          | SI LD integrators    | Lossless-Direct SI integrators            |

|                          | gm-C integrators     | Gm-C integrators                          |

|                          | gm-MC integrators    | Miller OTA integrators                    |

|                          | RC integrators       | Active-RC integrators                     |

|                          | MOSFET-C integrators | MOSFET-C integrators                      |

| Resonators               | SC FE resonators     | Resonators based on FE SC integrators     |

|                          | SC LD resonators     | Resonators based on LD SC integratorss    |

|                          | SI FE resonators     | Resonators based on FE SI integrators     |

|                          | SI LD resonators     | Resonators based on LD SI integrators     |

|                          | gm-C resonators      | Resonators based on Gm-C integrators      |

|                          | gm-LC resonators     | Resonators based on Gm-LC integrators     |

| Quantizers & Comparators | -                    | Nonideal single-bit & multibit quantizers |

Table 2.1 Overview of SIMSIDES libraries.

# **Building-Block Model Purpose and Description**

${\tt Ideal\_CT\_Integrator} \ \ block \ \ models \ \ the \ \ ideal \ S\text{-}domain \ \ transfer \ function \ of \ a \ CT \\ integrator, given by,$

$$ITF(s) = g \cdot \frac{1}{s} \tag{2.1}$$

Nonideal single-bit and multibit DACs

Adders, latches, DEM blocks, etc

where g stands for the integrator gain (also referred to as integrator weight). Ideal\_FE\_Integrator and Ideal\_LD\_Integrator blocks model the ideal Z-domain transfer functions of DT FE and LD integrators, respectively given by:

$$ITF_{FE}(z) = g \cdot \frac{z^{-1}}{1 - z^{-1}}$$

$$ITF_{LD}(z) = g \cdot \frac{z^{-1/2}}{1 - z^{-1}}$$

(2.2)

# **Model Parameters**

D/A Converters

**Auxiliary Blocks**

The following model parameters are included in the dialog box of the models above:

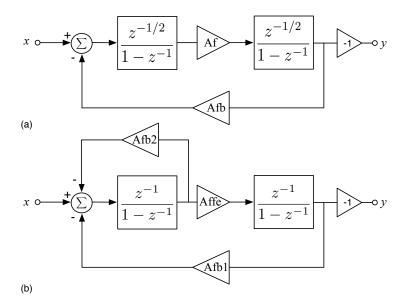

Figure 2.1 Z-domain block diagram of: (a) Ideal\_LD\_Resonator. (b) Ideal\_FE\_Resonator.

- Gain, which defines the integrator weight *g*.

- Sampling Time; i.e., the sampling period of both the Ideal\_FE\_Integrator and Ideal\_LD\_Integrator blocks.

# 2.2.2 Ideal Resonators

This library includes diverse ideal resonator blocks described below.

# Ideal\_LD\_Resonator

This block consists of a DT resonator made up of two LD integrators connected in a feedback loop as illustrated in Figure 2.1a. Its model parameters are the following:

- Af; i.e., the forward loop gain.

- Afb, which stands for the feedback loop gain.

- Sampling Time.

# Ideal\_FE\_Resonator

This block models a DT resonator made up of two FE integrators connected in a feedback loop as shown in Figure 2.1b. In this case, the model parameters are the following:

- Affe, which stands for the feed-forward loop gain.

- Afb1; i.e., the global feedback loop gain.

- Afb2; i.e., the local feedback loop gain.

- Sampling Time.

#### Ideal\_CT\_Resonator

This model corresponds to a CT (biquad) resonator with an S-domain transfer function given by:

$$RTF(s) = \frac{(\pi/2) \cdot s}{s^2 + (\pi/2)^2}$$

(2.3)

The above transfer function is implemented by using the Transfer Fcn block from the Continuous SIMULINK library.

# 2.2.3 Ideal Quantizers

This library includes several building blocks that model single-bit and multibit/multilevel quantizers intended for both voltage-mode (SC/CT) and current-mode (SI)  $\Sigma\Delta$ Ms.

# Ideal\_Comparator

This block models the input/output DC characteristic of an ideal comparator, given by a sign function as,

$$v_o = \begin{cases} V_{\text{high}} & v_i \ge 0 \\ V_{\text{low}} & v_i < 0 \end{cases}$$

(2.4)

where  $v_i$  and  $v_o$  stand for the input and output voltages, respectively, and  $V_{\text{high}}$  and  $V_{\text{low}}$  represent the analog values of the logic one and logic zero, respectively.

The model parameters of the Ideal\_Comparator block are the following:

- ullet Vhigh, Vlow, which stand respectively for  $V_{

m high}$  and  $V_{

m low}$

- Phase, which models the clock phase in which the input signal is sampled. Two nonoverlapping clock phases, denoted as phil, 2 are assumed.

- Sampling Time; i.e., the clock signal period.

- Identifier for this Quantizer, which defines an identification name for the block (used by some dynamic errors like the incomplete settling error in SC circuits).

# Ideal\_Comparator\_for\_SI

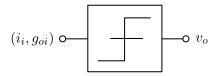

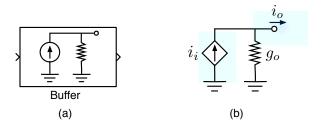

This block models a current-mode comparator used in  $SI-\Sigma\Delta Ms$ . The behavioral model is exactly the same as that used in the <code>Ideal\_Comparator</code> block, except that in this case the input signal is a current-mode signal that is modeled as a matrix made up of two vector elements, namely: the current signal itself and the output conductance of the current-mode building block (i.e, integrator, resonator, etc) connected at the input of the comparator.

This way, the information provided to the model at each sampling time is a vector of two elements as illustrated in Figure 2.2, where  $i_i$  is the input current,  $v_o$  is the output voltage, and  $g_{oi}$  is the output conductance of the building block connected at the comparator input.

Figure 2.2 Input and output signals in an Ideal\_Comparator\_for\_SI model.

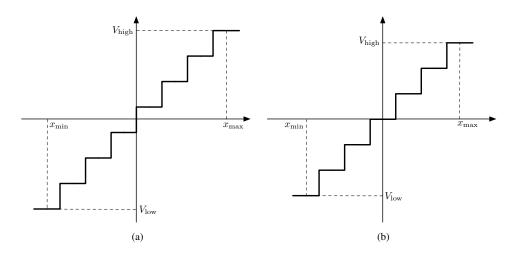

**Figure 2.3** Illustrating the input/output DC characteristic of: (a) Multibit (3-bit) *midrise* quantizer. (b) Multilevel (7-level) *midtreat* quantizer.

# $Ideal\_Multibit\_Quantizer$

This building block includes the ideal behavioral model of a multibit quantizer with a DC input/output *midrise* characteristic as illustrated in Figure 2.3a.

The model parameters of this block are the following ones:

- Vhigh, Vlow, which stand respectively for the maximum and minimum values of the quantizer output FS range–see Figure 2.3a.

- Number of bits of the quantizer.

- Xmax-Xmin, that defines the input FS range of the quantizer.

- Phase ON, which is the clock phase in which the input signal is sampled, considering a two-phase clock signal generator.

- Sampling Time, that denotes the clock period.

# Ideal\_Multibit\_Quantizer\_for\_SI

This block models a current-mode multibit quantizer with the same input/output characteristic as an Ideal\_Multibit\_Quantizer, but considering that the input signal has two components- $i_i$  and  $g_{oi}$ -in the same way as in Figure 2.2.

#### Ideal\_Multibit\_Quantizer\_levels

This building block models a multilevel quantizer in which the input/output characteristic is defined as a function of the number of levels, instead of the number of bits as in the Ideal\_Multibit\_Quantizer block. Thus, the same parameters are used, except for the number of bits, which is replaced by Number of levels. If this parameter is even, a *midrise* quantization characteristic like that shown in Figure 2.3a is implemented. Otherwise, a *midtreat* characteristic like that depicted in Figure 2.3b is provided.

# Ideal\_Multibit\_Quantizer\_levels\_SD2

This building block includes the same behavioral model as the previous one, but the output is a thermometric-coded bit array. This is used in combination with multilevel DACs with DEM techniques, as will be illustrated in Section 2.8.

# Ideal\_Sampler

This building block models an ideal S&H circuit which can be used in CT- $\Sigma\Delta$ Ms, in which the signal is sampled at the input of internal quantizers.

Their model parameters are the following:

- Sampling Time, that denotes the clock period.

- Input clock phase, which defines the sampling clock phase.

# 2.2.4 Ideal D/A Converters

The blocks included in this library model different kinds of ideal DACs, namely:

- Ideal\_DAC, which is used for modeling ideal single-bit DACs for either SC- or CT- $\Sigma\Delta$ Ms. They are simply modeled as a voltage gain, named Gain in the model.

- Ideal\_DAC\_for\_SI, which models a single-bit DAC for SI- $\Sigma\Delta Ms$ .

- Ideal\_DAC\_dig\_level\_SD2, which consists of a multilevel ideal DAC.

The last two models and their associated parameters are described below.

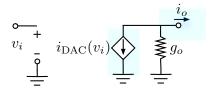

### Ideal\_DAC\_for\_SI

Figure 2.4 shows the equivalent circuit of the Ideal\_DAC\_for\_SI block. It consists of a voltage-controlled current source in parallel with a finite output conductance  $g_o$ . The current source  $i_{DAC}$  is a sign function of the input voltage  $v_i$  given by,

Figure 2.4 Equivalent circuit of Ideal\_DAC\_for\_SI model.

$$i_{DAC}(v_i) = \begin{cases} +I_{ref} & v_i = +v_{ref} \\ -I_{ref} & v_i = -v_{ref} \end{cases}$$

(2.5)

where  $I_{\text{ref}}$  and  $v_{\text{ref}}$  stand for the modulator FS reference current and voltage, respectively. The model parameters included in the Ideal\_DAC\_for\_SI model are the following:

- ullet Gain, which models the DAC gain; i.e.,  $I_{\rm ref}/v_{\rm ref}$ .

- Gout, which stands for  $g_o$ .

- Sampling Time, which models the clock period.

- Input Clock Phase; i.e., the clock phase at which the DAC input is sampled.

# Ideal\_DAC\_dig\_level\_SD2

This block transforms a thermometric-coded digital input into its corresponding analog level. The model parameters used in this behavioral model are:

- Vhigh, which defines the upper limit of the quantization FS range.

- Vlow, which corresponds to the lower limit of the quantization FS range.

- Number of levels of the embedded quantizer.

# 2.3 Real SC Building-Block Libraries

SIMSIDES includes two libraries of SC integrators and two libraries of SC resonators. These libraries are described below.

# 2.3.1 Real SC Integrators

There are two SC integrator model libraries in SIMSIDES: one including FE SC integrator models and the other one including LD SC integrators. In both cases, integrator models are classified according to the nonideal effects that are included in the model and the number of SC branches connected at the integrator input. This way, for each model there are four building blocks using the same behavioral model except for the number of input SC branches.

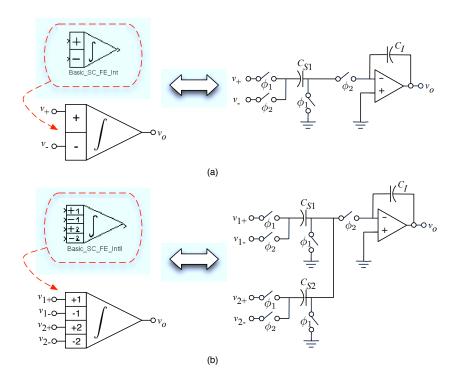

As an illustration, Figure 2.5 shows the symbol used in SIMSIDES for one-branch SC FE integrators (Figure 2.5a) and two-branch SC FE integrators (Figure 2.5b), together with their

Figure 2.5 SC integrator symbol in SIMSIDES: (a) One-branch integrator. (b) Two-branch integrator.

equivalent SC circuits. Note that, although single-ended conceptual schematics are shown in this figure, fully-differential circuits are assumed in the behavioral models.

Both integrators in Figure 2.5 use the same behavioral model, which consists of an ideal SC FE integrator with output swing limitation. The behavioral model corresponding to a one-branch SC FE integrator is named <code>Basic\_SC\_FE\_Int</code>, while the model of the two-branch SC FE integrator is named <code>Basic\_SC\_FE\_IntII</code>. Following this nomenclature, <code>Basic\_SC\_FE\_IntIII</code> and <code>Basic\_SC\_FE\_IntIV</code> models are used for three- and four-branch SC FE integrators, respectively.

Table 2.2 lists all SC integrator models available in SIMSIDES including a brief description of the nonidealities included in each of them. Note that the model names included in Table 2.2 correspond to one-branch integrators. The same models are available for integrators with up to four input branches.

The model named  $SC_FE_Int_1b_SD2$  represents one-branch SC FE integrators with all circuit nonidealideal effects, including the degradation caused by the switch on-resistance on the integrator GB and SR. In this model, notation 1b is used for denoting one input SC branch. Similarly, other models whose names include nb denote n input SC branches.

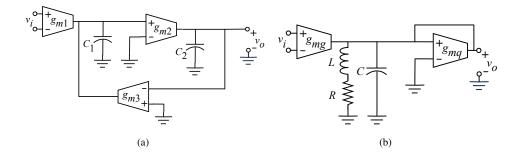

The model named SC\_FE\_Int\_1b\_DEM\_SD2 includes the same nonideal effects as SC\_FE\_Int\_1b\_SD2 model but it also allows to model the sampling capacitor as an array of unit capacitors. This array is used in combination with multilevel quantizers and DACs which incorporate DWA/DEM algorithms as described in [1]. This way, the number

of unit capacitors in the array must be exactly the same as the number of DAC levels. Moreover, this array should include the DAC mismatch error, which can be modeled as a Gaussian distribution. Both SC\_FE\_Int\_1b\_SD2 and SC\_FE\_Int\_1b\_DEM\_SD2 models provide detailed information about the integrator equivalent input-referred thermal noise, equivalent load capacitances, and transient response model parameters. All these pieces of information are displayed in the MATLAB command window after simulation.

Table 2.3 lists the most important parameters used by the SC integrator behavioral models in SIMSIDES, as well as a brief description of all of them.

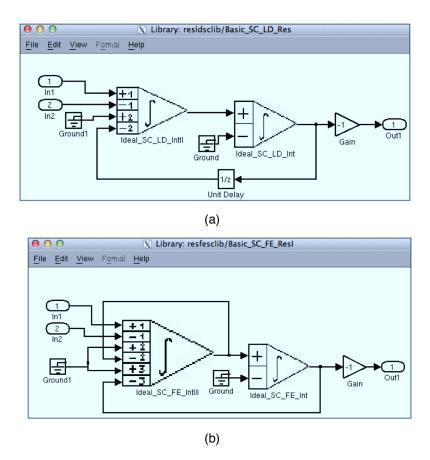

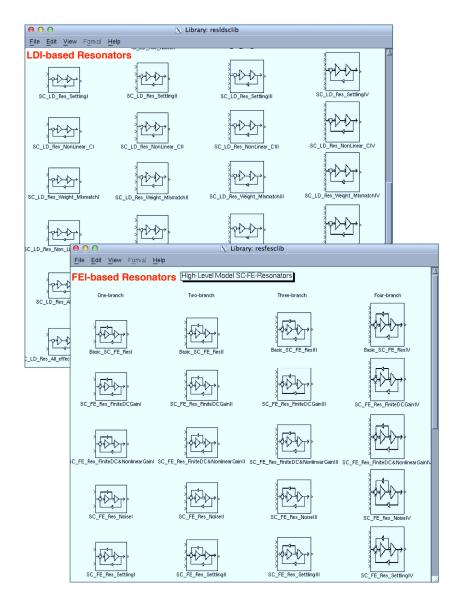

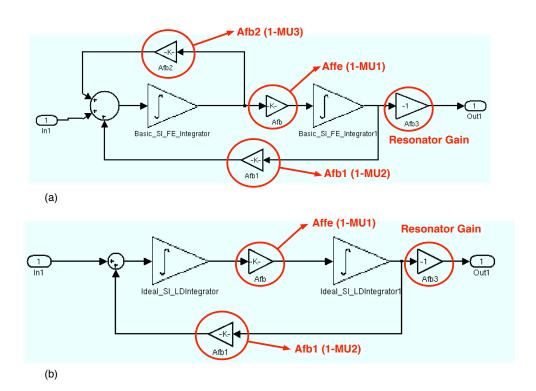

#### 2.3.2 Real SC Resonators

SIMSIDES has two SC resonator model libraries corresponding to FEI-based resonators and LDI-based resonators. All building-block models correspond to the Z-domain block diagrams shown in Figure 2.1 but they are implemented by using the SC integrator models described in the previous section. As an illustration, Figure 2.6 shows the SIMSIDES block diagram of an SC LDI-based resonator (Figure 2.6a) and an SC FEI-based resonator (Figure 2.6b), which correspond to Figures 2.1a and 2.1b, respectively.

Following the same philosophy as that used in SC integrators, the behavioral models of SC resonators in SIMSIDES are classified attending to the number of input SC branches and the circuit nonideal effects included in the models. As an illustration, Figure 2.7 shows an excerpt of both SC resonators libraries. Note that each row of blocks include the same circuit nonideal effects, with the only difference among them being the number of input branches.

Table 2.4 lists all SC resonator models available in SIMSIDES, including a brief description of the nonidealities considered in each of them. The parameters used in these models are the same as those included in SC integrator models—listed in Table 2.3. In addition to these parameters, the resonator gain can also be defined by the user by setting a parameter named Gain (see Figure 2.6), which can be defined in the model dialogue box.

### 2.4 Real SI Building-Block Libraries

SIMSIDES includes all necessary building blocks for the simulation of SI- $\Sigma\Delta$ Ms. This section describes SI integrators and resonators, as well as their main model parameters.

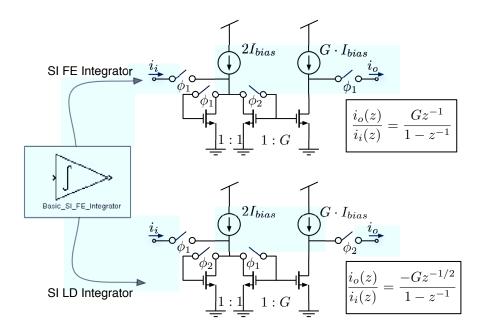

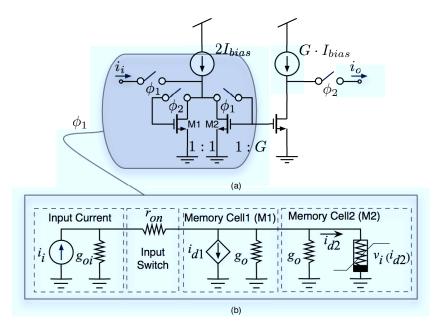

#### 2.4.1 Real SI Integrators

Following the same classification criteria as that followed for SC building-block models, there are two libraries of SI integrators in SIMSIDES: one including FE SI integrators and the other one including LD SI integrators. Figure 2.8 shows the symbol used in SIMSIDES for SI integrators together with a conceptual schematic of a FE SI integrator and a LD SI integrator. In both cases, different models are included in SIMSIDES, which are classified attending to the number of nonideal effects that are taken into account, as detailed in Table 2.5.

Apart from the building blocks in Table 2.5, a current-mode *buffer* block, named <code>Buffer</code>, is included in all SIMSIDES SI libraries. This block transforms an input current vector into an output matrix made up of two vector elements: the input current signal itself in parallel with an output conductance, named <code>Gout of the source</code> in the model. Figure 2.9 illustrates

Table 2.2

Library of SC (FE/LD) integrators included in SIMSIDES.

| Model name                                                                         | Circuit effects included                                                                                                                                                                                                                 |

|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Basic_SC_FE_Int<br>Basic_SC_LD_Int                                                 | Output swing limitation                                                                                                                                                                                                                  |

| SC_FE_Int_Non_linear_C SC_LD_Int_Non_linear_C                                      | Output swing limitation, capacitor nonlinearity.                                                                                                                                                                                         |

| SC_FE_Int_Weight_Mismatch SC_LD_Int_Weight_Mismatch                                | Output swing limitation, capacitor mismatch.                                                                                                                                                                                             |

| SC_FE_Int_Non_Linear_Sampling SC_LD_Int_Non_Linear_Sampling                        | Output swing limitation, nonlinear switch on-resistance.                                                                                                                                                                                 |

| SC_FE_Int_FiniteDCgain<br>SC_LD_Int_FiniteDCgain                                   | Finite OTA DC gain,<br>output swing limitation,<br>parasitic OTA caps.                                                                                                                                                                   |

| SC_FE_Int_Finite&Non_LinearDCGain<br>SC_LD_Int_Finite&Non_LinearDCGain             | Finite nonlinear OTA DC gain, output swing limitation parasitic OTA caps.                                                                                                                                                                |

| SC_FE_Int_Noise<br>SC_LD_Int_Noise                                                 | OTA thermal noise, output swing limitation, parasitic/load OTA caps.                                                                                                                                                                     |

| SC_FE_Int_Settling<br>SC_LD_Int_Settling                                           | Incomplete settling error, output swing limitation, parasitic/load OTA caps.                                                                                                                                                             |

| SC_FE_Integrator_All_Effects SC_LD_Integrator_All_Effects                          | switch on-resistance,<br>capacitor nonlinearity and mismatch,<br>settling error, finite (nonlinear) DC gain,<br>thermal noise, parasitic/load capacitors,<br>output swing limitation.                                                    |

| SC_FE_Integrator_All_Effects&NonLinSamp<br>SC_LD_Integrator_All_Effects&NonLinSamp | switch nonlinear on-resistance, capacitor nonlinearity and mismatch, settling error, finite (nonlinear) DC gain, thermal noise, parasitic/load capacitors, output swing limitation.                                                      |

| SC_FE_Int_1b_SD2                                                                   | switch on-resistance and its effect on GB and SR, capacitor nonlinearity and mismatch, settling error, finite (nonlinear) DC gain, thermal noise, parasitic/load capacitors, output swing limitation.                                    |

| SC_FE_Int_1b_DEM_SD2                                                               | switch on-resistance and its effect on GB and SR, array of unit sampling capacitors, capacitor nonlinearity and mismatch, settling error, finite (nonlinear) DC gain, thermal noise, parasitic/load capacitors, output swing limitation. |

Table 2.3

Model parameters used in SIMSIDES SC (FE/LD) integrators.

| Array of sampling capacitors for DEM branch  B (switch parameters)  Bandwidth (BW)  Capacitor (first/second) - order capacitors with on-resistance, linear model of the sinewave input (table look-up model)  Input signal bandwidth  Capacitor (first/second) - order capacitor order nonlinearity  Finite and Linear Ron  Finite DC Gain of the AO  g (switch parameters)  Identifier used for settling error model  Input Equivalent Thermal Noise  Input parameters [A, fi, ph] (switch)  Integration/Sampling Capacitor  Integration/sampling capacitors  Integration additional load  Maximum output current (Io)  Nonlinearity of the DC Gain  Otta DC gain nonlinear coefficients  Maximum output current  Otta DC gain nonlinear coefficients  Additional load capacitance at the OTA input parameters of the Since was provided in the since and the composition of the switch on-resistance (table look-up model)  Parasitic Capacitor before the AO (Cp)  Parasitic capacitance at the OTA input swing limit provided in the switch on-resistance (table look-up model)  Positive Input is Sampled in  Input-switch on-resistance  Sampling additional load  Additional load capacitance at the Sampling phase  Clock signal period  Switch on-resistance  Additional resistance  Temp  Tempe  Temperature (K)  OTA transconductance | 1                                           | ` , e                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|------------------------------------------|

| for DEM branch  B (switch parameters)  Bandwidth (BW)  Capacitor (first/second)-order (Capacitor (first/second) (order nonlinearity)  Finite and Linear Ron  Finite DC Gain of the AO  g (switch parameters)  Tenjut Equivalent Thermal Noise  Input Equivalent Thermal Noise  Input parameters [A, fi, ph] (switch)  Integration/Sampling Capacitor  Integration/Sampling Capacitor  Integration additional load  Maximum output current (Io)  Nonlinearity of the DC Gain  OTA DC gain put-referred thermal noise  Amplitude, frequency, and phase of the sinewave input (table look-up model)  Integration additional load  Additional load capacitance at the integration phase  Load Capacitor (cload)  Integration output current (Io)  Nonlinearity of the DC Gain  OTA DC gain nonlinear coefficients  Output Swing Up/Down  Parasitic Capacitor before the AO (Cp)  Parasitic capacitance at the OTA input pooef (switch parameters)  Roo  Sampling additional load  Additional load capacitance  Additional load capacitance at the OTA input pooef (switch parameters)  Nonlinear coefficients of the switch on-resistance  (table look-up model)  Positive Input is Sampled in  Input-switch clock phase  Switch on-resistance  Sampling additional load  Additional load capacitance at the sampling phase  Clock signal period  Switch on-resistance  Temp  Temperature (K)  Transconductance of the AO (gm)  OTA transconductance                | Parameter name (in alphabetical order)      | Brief description                        |

| Bandwidth (BW)  Capacitor (first/second) - order Capacitor (first/second) order nonlinearity  Finite and Linear Ron Switch on-resistance, linear model  Finite DC Gain of the AO Finite OTA DC gain  g (switch parameters) Finite switch on-conductance (analytic model)  Identifier for this integrator Identifier used for settling error model  Input Equivalent Thermal Noise OTA input-referred thermal noise  Input parameters [A, fi, ph] (switch) Amplitude, frequency, and phase of the sinewave input (table look-up model)  Integration/Sampling Capacitor Integration/sampling capacitors  Integration additional load Additional load capacitance at the integration phase  Load Capacitor (cload) Integrator load capacitance  Maximum output current (Io) OTA maximum output current  Output Swing Up/Down Maximum/minimum output swing limi  Parasitic Capacitor before the AO (Cp) Parasitic capacitance at the OTA input  pcoef (switch parameters) nonlinear coefficients of the switch on-resistance  (table look-up model)  Positive Input is Sampled in Input-switch clock phase  Ron Switch on-resistance  Sampling additional load Additional load capacitance at the sampling phase  Clock signal period  Switch on-resistance  Finite Signal period  Switch on-resistance  Tempo Temporature (K)  OTA transconductance                                                                                                                | Array of sampling capacitors for DEM branch | •                                        |

| Capacitor (first/second) - order nonlinearity order nonlinearity  Finite and Linear Ron switch on-resistance, linear model  Finite DC Gain of the AO Finite OTA DC gain  g (switch parameters) Finite switch on-conductance (analytic model)  Identifier for this integrator Identifier used for settling error model  Input Equivalent Thermal Noise OTA input-referred thermal noise  Input parameters [A, fi, ph] (switch) Amplitude, frequency, and phase of the sinewave input (table look-up model)  Integration/Sampling Capacitor Integration/sampling capacitors  Integration additional load Additional load capacitance at the integration phase  Load Capacitor (cload) Integrator load capacitance  Maximum output current (Io) OTA maximum output current  Nonlinearity of the DC Gain OTA DC gain nonlinear coefficients  Output Swing Up/Down Maximum/minimum output swing limity  Parasitic Capacitor before the AO (Cp) Parasitic capacitance at the OTA input procef (switch parameters) nonlinear coefficients of the switch on-resistance (table look-up model)  Positive Input is Sampled in Input-switch clock phase  Sampling additional load Additional load capacitance at the sampling phase  Sampling Time Clock signal period  Switch on-resistance  Temp Temperature (K)  Transconductance of the AO (gm) OTA transconductance                                                                                                    | B (switch parameters)                       |                                          |

| ronlinearity  Finite and Linear Ron  Finite DC Gain of the AO  Finite DC Gain of the AO  Finite DC Gain of the AO  Finite Switch on-conductance (analytic model)  Identifier for this integrator  Identifier used for settling error model  Input Equivalent Thermal Noise  OTA input-referred thermal noise  Input parameters [A, fi, ph] (switch)  Integration/Sampling Capacitor  Integration additional load  Additional load capacitance at the integration phase  Load Capacitor (cload)  Integration output current (IO)  Nonlinearity of the DC Gain  Ota DC gain nonlinear coefficients  Output Swing Up/Down  Parasitic Capacitor before the AO (Cp)  Parasitic capacitance at the OTA input  pcoef (switch parameters)  Ron  Sampling additional load  Additional load capacitance  Maximum/minimum output swing limi  procef (switch parameters)  Input-switch on-resistance  (table look-up model)  Positive Input is Sampled in  Input-switch clock phase  Sampling additional load  Additional load capacitance  at the switch on-resistance  Sampling Time  Clock signal period  Switch on-resistance  Temp  Tempo  Tempo  Tempo  OTA transconductance                                                                                                                                                                                                                                                                                          | Bandwidth (BW)                              | Input signal bandwidth                   |

| Finite DC Gain of the AO  Finite OTA DC gain  Finite witch on-conductance (analytic model)  Identifier for this integrator  Identifier used for settling error model  Input Equivalent Thermal Noise  OTA input-referred thermal noise  Input parameters [A, fi, ph] (switch)  Integration/Sampling Capacitor  Integration/Sampling Capacitor  Integration additional load  Additional load capacitance  At the integration phase  Load Capacitor (cload)  Integrator load capacitance  Maximum output current (Io)  OTA maximum output current  Nonlinearity of the DC Gain  OTA DC gain nonlinear coefficients  Output Swing Up/Down  Parasitic Capacitor before the AO (Cp)  Parasitic capacitance at the OTA input  pcoef (switch parameters)  nonlinear coefficients of the switch on-resistance (table look-up model)  Positive Input is Sampled in  Input-switch clock phase  Sampling additional load  Additional load capacitance at the sampling phase  Sampling Time  Clock signal period  Switch on-resistance  Temp  Temperature (K)  OTA transconductance                                                                                                                                                                                                                                                                                                                                                                                         | Capacitor (first/second)-order nonlinearity |                                          |

| Finite switch on-conductance (analytic model)  Identifier for this integrator Identifier used for settling error model  Input Equivalent Thermal Noise OTA input-referred thermal noise  Input parameters [A, fi, ph] (switch) Amplitude, frequency, and phase of the sinewave input (table look-up model)  Integration/Sampling Capacitor Integration/sampling capacitors  Integration additional load Additional load capacitance at the integration phase  Load Capacitor (cload) Integrator load capacitance  Maximum output current (Io) OTA maximum output current  Nonlinearity of the DC Gain OTA DC gain nonlinear coefficients  Output Swing Up/Down Maximum/minimum output swing limi  Parasitic Capacitor before the AO (Cp) Parasitic capacitance at the OTA input  pcoef (switch parameters) nonlinear coefficients of the switch on-resistance (table look-up model)  Positive Input is Sampled in Input-switch clock phase  Ron switch on-resistance  Sampling additional load Additional load capacitance at the sampling phase  Sampling Time Clock signal period  Switch on-resistance  Temp Temperature (K)  Transconductance of the AO (gm) OTA transconductance                                                                                                                                                                                                                                                                           | Finite and Linear Ron                       | switch on-resistance, linear model       |

| (analytic model)  Identifier for this integrator Identifier used for settling error model  Input Equivalent Thermal Noise OTA input-referred thermal noise  Input parameters [A, fi, ph] (switch) Amplitude, frequency, and phase of the sinewave input (table look-up model)  Integration/Sampling Capacitor Integration/sampling capacitors  Integration additional load Additional load capacitance at the integration phase  Load Capacitor (cload) Integrator load capacitance  Maximum output current (Io) OTA maximum output current  Nonlinearity of the DC Gain OTA DC gain nonlinear coefficients  Output Swing Up/Down Maximum/minimum output swing limit parasitic Capacitor before the AO (Cp) Parasitic capacitance at the OTA input proof (switch parameters) nonlinear coefficients of the switch on-resistance (table look-up model)  Positive Input is Sampled in Input-switch clock phase  Ron Switch on-resistance  Sampling additional load Additional load capacitance at the sampling phase  Sampling Time Clock signal period  Switch on-resistance  Temp Temperature (K)  Transconductance of the AO (gm) OTA transconductance                                                                                                                                                                                                                                                                                                         | Finite DC Gain of the AO                    | Finite OTA DC gain                       |

| Input Equivalent Thermal Noise  Input parameters [A, fi, ph] (switch)  Integration/Sampling Capacitor  Integration additional load  Additional load capacitance at the integration phase  Load Capacitor (cload)  Integrator load capacitance  Maximum output current (Io)  OTA maximum output current  Nonlinearity of the DC Gain  Ota DC gain nonlinear coefficients  Output Swing Up/Down  Parasitic Capacitor before the AO (Cp)  Parasitic capacitance at the OTA input  pcoef (switch parameters)  nonlinear coefficients of the switch on-resistance (table look-up model)  Positive Input is Sampled in  Ron  Sampling additional load  Additional load capacitance at the Sampling phase  Sampling Time  Clock signal period  Switch on-resistance  Temp  Temperature (K)  Transconductance of the AO (gm)  OTA transconductance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | g (switch parameters)                       |                                          |

| Input parameters [A, fi, ph] (switch)  Amplitude, frequency, and phase of the sinewave input (table look-up model)  Integration/Sampling Capacitor  Integration additional load  Additional load capacitance at the integration phase  Load Capacitor (cload)  Maximum output current (Io)  OTA maximum output current  Nonlinearity of the DC Gain  OTA DC gain nonlinear coefficients  Output Swing Up/Down  Parasitic Capacitor before the AO (Cp)  Parasitic capacitance at the OTA input  pcoef (switch parameters)  nonlinear coefficients of the switch on-resistance (table look-up model)  Positive Input is Sampled in  Ron  Sampling additional load  Additional load capacitance at the sampling phase  Sampling Time  Clock signal period  Switch on-resistance  Temp  Temperature (K)  Transconductance of the AO (gm)  OTA transconductance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Identifier for this integrator              | Identifier used for settling error model |

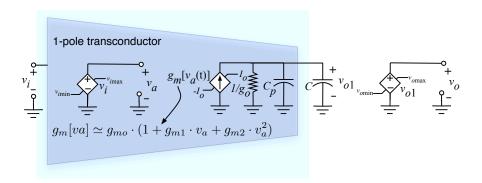

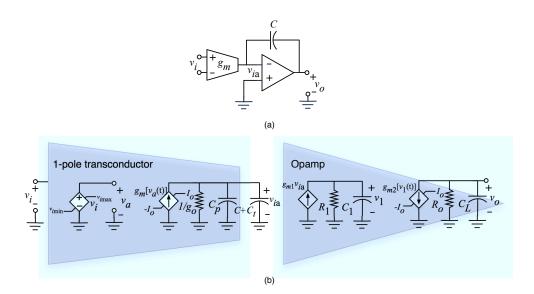

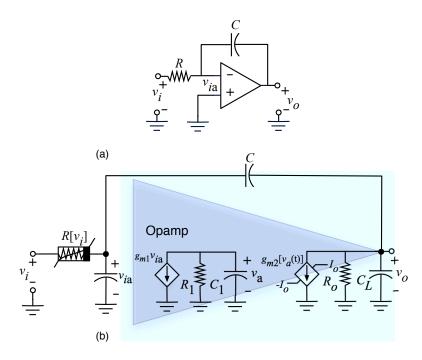

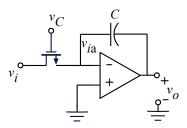

| the sinewave input (table look-up model)  Integration/Sampling Capacitor  Integration additional load  Additional load capacitance at the integration phase  Load Capacitor (cload)  Integrator load capacitance  Maximum output current (Io)  OTA maximum output current  Nonlinearity of the DC Gain  OTA DC gain nonlinear coefficients  Output Swing Up/Down  Maximum/minimum output swing limit  Parasitic Capacitor before the AO (Cp)  Parasitic capacitance at the OTA input  pcoef (switch parameters)  nonlinear coefficients of the switch on-resistance (table look-up model)  Positive Input is Sampled in  Input-switch clock phase  Ron  Switch on-resistance  Additional load capacitance at the sampling phase  Sampling additional load  Additional load capacitance at the sampling phase  Clock signal period  Switch on-resistance  Temp  Temperature (K)  Transconductance of the AO (gm)  OTA transconductance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Input Equivalent Thermal Noise              | OTA input-referred thermal noise         |